# N32H47X/N32H48X系列硬件设计指南

简介

本文档详细介绍 N32H47X/N32H48X 系列 MCU 硬件设计检查列表,以 便为用户提供硬件设计指导。

国民技术 版权所有

# 目录

| 1. | N32H47X/N32H48X 系列 MCU 硬件设计检查列表3 |                       |    |  |  |  |  |  |  |

|----|----------------------------------|-----------------------|----|--|--|--|--|--|--|

|    | 1.1                              | 电源供电简介                | 3  |  |  |  |  |  |  |

|    | 1.2                              | 供电方案                  | 3  |  |  |  |  |  |  |

|    | 1.3                              | 备用电池                  | 3  |  |  |  |  |  |  |

|    | 1.4                              | 外部引脚复位电路              | 3  |  |  |  |  |  |  |

|    | 1.5                              | 外部时钟电路                | 4  |  |  |  |  |  |  |

|    | 1.6                              | 启动引脚连接                | 4  |  |  |  |  |  |  |

|    | 1.7                              | ADC 转换器               | 4  |  |  |  |  |  |  |

|    | 1.8                              | PGA 应用参考              | 6  |  |  |  |  |  |  |

|    | 1.8.1                            | 单端模式应用                | 6  |  |  |  |  |  |  |

|    | 1.8.2                            | 差分模式应用                | 7  |  |  |  |  |  |  |

|    | 1.8.3                            | PGA 使用注意事项            | 9  |  |  |  |  |  |  |

|    | 1.9                              | IO 上电脉冲处理             | 9  |  |  |  |  |  |  |

|    | 1.10                             | IO 耐压值                | 10 |  |  |  |  |  |  |

|    | 1.11                             | 防静电设计                 | 11 |  |  |  |  |  |  |

|    | 1.11.                            | 1 PCB 设计              | 11 |  |  |  |  |  |  |

|    | 1.11.2                           | 2 ESD 防护器件            | 11 |  |  |  |  |  |  |

|    | 1.12                             | 调试接口                  | 11 |  |  |  |  |  |  |

|    | 1.13                             | BOOT 串口接口             | 12 |  |  |  |  |  |  |

| 2. | 整体设计                             | 建议                    | 13 |  |  |  |  |  |  |

| 3. | 最小系统                             | 参考设计原理图               | 14 |  |  |  |  |  |  |

|    | 3.1                              | UQFN32-N32H473KEU7    | 14 |  |  |  |  |  |  |

|    | 3.2                              | LQFP48-N32H473CEL7    | 15 |  |  |  |  |  |  |

|    | 3.3                              | LQFP48-N32H474CEL7    | 16 |  |  |  |  |  |  |

|    | 3.4                              | QFN48-N32H473CGQ8     | 17 |  |  |  |  |  |  |

|    | 3.5                              | UQFN48-N32H473CEU7    | 18 |  |  |  |  |  |  |

|    | 3.6                              | UQFN48-1-N32H473CCU7E | 19 |  |  |  |  |  |  |

|    | 3.7                              | UQFN48-N32H474CEU7    | 20 |  |  |  |  |  |  |

|    | 3.8                              | QFN52-N32H475UEQ7S    | 21 |  |  |  |  |  |  |

|    | 3.9                              | QFN60-N32H475REQ7     | 22 |  |  |  |  |  |  |

|    | 3.10                             | LQFP64-N32H473REL7    | 23 |  |  |  |  |  |  |

|    | 3.11                             | LQFP64-N32H474REL7    | 24 |  |  |  |  |  |  |

|    | 3.12                             | LQFP64-N32H481REL7K   | 25 |  |  |  |  |  |  |

|    | 3.13                             | LQFP64-N32H488REL7K   | 26 |  |  |  |  |  |  |

|    | 3.14                             | LQFP64-N32H482REL7    | 27 |  |  |  |  |  |  |

|    |                                  |                       |    |  |  |  |  |  |  |

|    | 3.15    | LQFP64-N32H487REL7  | 28 |

|----|---------|---------------------|----|

|    | 3.16    | LQFP64-N32H488REL7  | 29 |

|    | 3.17    | LQFP80-N32H473MEL7  | 30 |

|    | 3.18    | LQFP80-N32H474MEL7  | 31 |

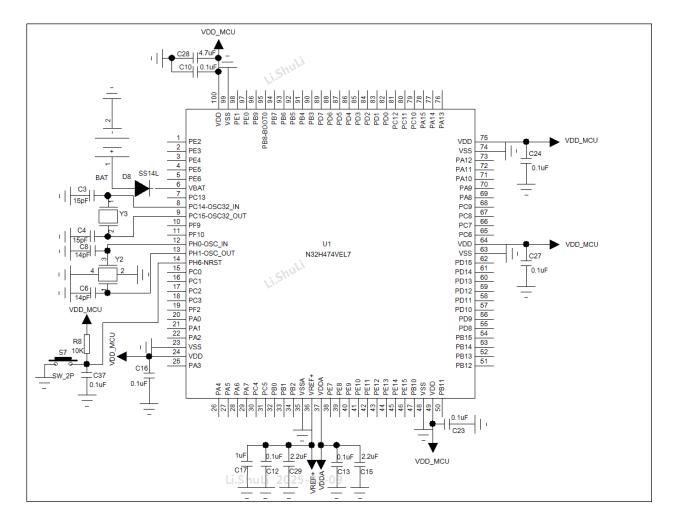

|    | 3.19    | LQFP100-N32H474VEL7 | 32 |

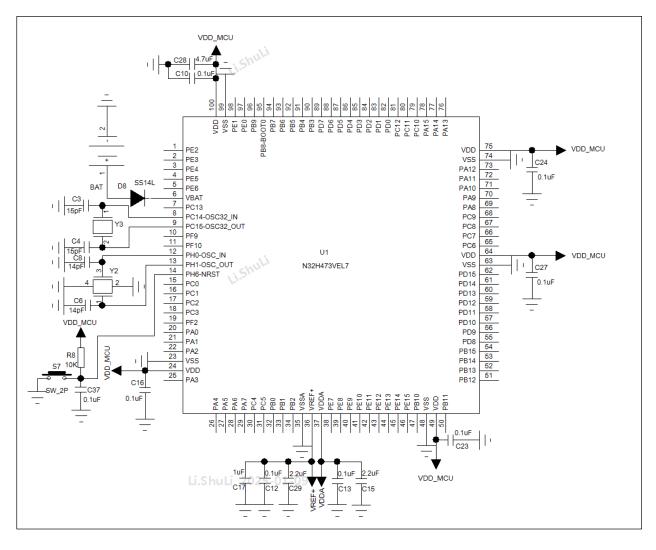

|    | 3.20    | LQFP100-N32H473VEL7 | 33 |

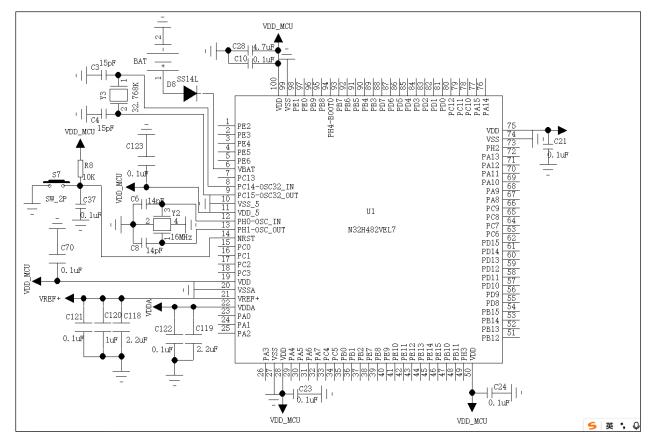

|    | 3.21    | LQFP100-N32H482VEL7 | 34 |

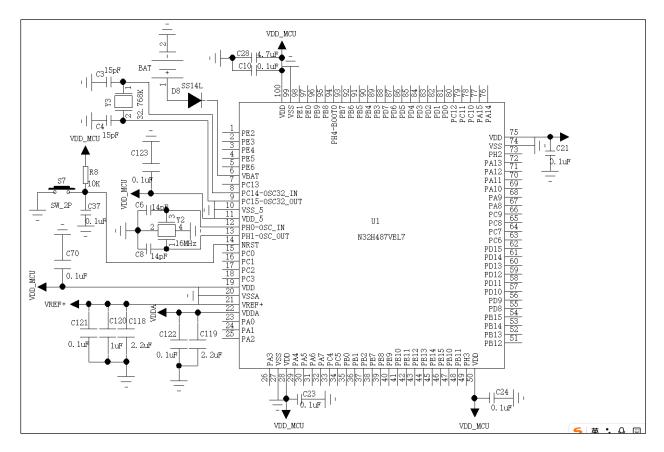

|    | 3.22    | LQFP100-N32H487VEL7 | 35 |

|    | 3.23    | LQFP100-N32H488VEL7 | 36 |

|    | 3.24    | LQFP128-N32H474QEL7 | 37 |

|    | 3.25    | LQFP128-N32H473QEL7 | 38 |

|    | 3.26    | LQFP144-N32H482ZEL7 | 39 |

|    | 3.27    | LQFP144-N32H487ZEL7 | 40 |

|    | 3.28    | LQFP144-N32H488ZEL7 | 41 |

| 4. | PCB LAY | OUT 参考              | 42 |

| 5. | 历史版本.   |                     | 43 |

| 6  | 古 田     |                     | 11 |

### 1. N32H47X/N32H48X 系列 MCU 硬件设计检查列表

## 1.1 电源供电简介

N32H47X/N32H48X 系列芯片工作电压(VDD)为 1.8V~3.6V。主要有: VDD、VDDA、VBAT 引脚。具体请参考相关数据手册。

### 1.2 供电方案

VDD 为 MCU 主电源,必须由稳定的外部电源供电。电压范围 1.8V~3.6V,所有 VDD 引脚都需就近放置一颗 0.1uF 去耦电容,其中一个 VDD 管脚还需增加一颗 4.7uF 去耦电容。去耦电容具体设计请参考第三章节各封装最小系统参考设计原理图.

VDDA 为模拟电源,为 ADC、DAC、COMP、PGA 提供供电。VDDA 输入管脚建议放置一个 0.1uF 和一个 2.2uF 的电容。

VREF+为参考电压,为 ADC、DAC 提供参考电平,当 VERF+使用内置参考源 VREFBUF 时,VREF+引脚建议就近放置一个 0.1uF 和一个 1uF 的电容。当 VERF+由外部供电时,VREF+引脚建议就近放置一个 0.1uF 和一个 2.2uF 的电容。

注: VREFBUF 严禁在内部输出模式的同时开启外部输入,输出模式与外部输入模式只能二选一。

### 1.3 备用电池

VBAT 引脚主要给备电域(RTC、LPTIM、Backup SRAM)供电,使得备电域模块在主电源(VDD)关闭时仍能正常运行。

### 1.4 外部引脚复位电路

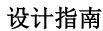

当NRST引脚上出现低电平(外部复位)将产生系统复位。外部NRST引脚复位参考电路如下。

图 1-1 系统复位图

注:复位引脚NRST在设计时建议不悬空,外挂电容0.1uF作为典型参考值给出,若需加快复位时间,NRST引脚可外加上拉,另外用户可根据产品实际需要决定是否增加复位按键。

### 1.5 外部时钟电路

N32H47X/N32H48X 系列 MCU 包含 2 个外部时钟: 外部高速时钟 HSE (4MHz~32MHz) 和外部低速时钟 LSE (通常使用 32.768KHz)。

HSE 和 LSE 根据晶振特性配置相应的负载电容,详细请参考相关数据手册中外部时钟特性描述。

### 1.6 启动引脚连接

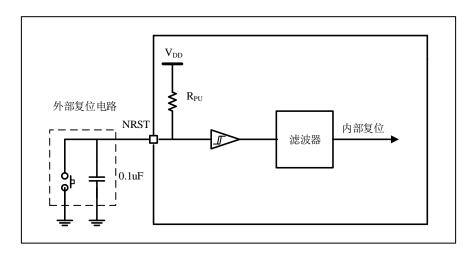

下图显示了 N32H47X/N32H48X 系列芯片选择启动存储器时所需的外部连接。关于启动模式请参考用户手册相关章节。

图 1-2 启动模式实现实例

BOOT引脚拉高,芯片复位后从BOOT区启动;BOOT引脚拉低,芯片复位后从用户区启动。

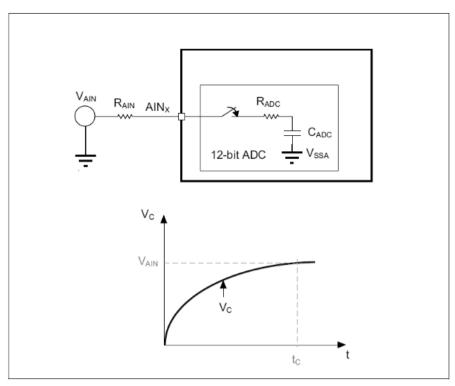

### 1.7 ADC 转换器

关于 ADC 电路设计,请注意如下几点:

- 1) 在使用 ADC 采样时,建议缩短 ADC 采样通道的外部走线距离;

- 2) ADC 的输入信号周边建议远离一些高频翻转信号;

- 3) 注意慢速通道和快速通道的最高支持速率:

N32H47X/N32H48X 系列在 ADC 输入时钟为 80MHZ 条件下,ADC 快速通道采样率不超过 4.7Msps,ADC 慢速通道采样率建议不超过 2.5Msps;

4) 在 ADC 转换期间,芯片不支持修改 ADC 配置,如需修改配置,需要等待当前转换结束或者关闭 ADC 后,再进行配置;

- 5) 在使用某一 ADC 通道时,不能在其它未使用的 ADC 采样通道施加负压(比如-0.2V),如果施加了此负电压,会导致正常采样的 ADC 通道电压被拉低,导致读取的数据不准;

- 6) 在使用某一 ADC 通道时,不能在其它未使用的 ADC 采样通道施加高压 (大于 VDD 电压),如果施加了此高电压,会导致正常采样的 ADC 通道电压被拉高,导致读取的数据不准;

- 7) 在使用 ADC 时,ADC 的采样速率和 R<sub>AIN</sub> 是相关的,R<sub>AIN</sub> 越小采样速率越快,具体见下表:

图 1-3 ADC 输入口串联电阻的影响

#### ADC 采样时间表:

| 八分位             | D (10)                 | 最小采样时间(ns) |        |  |

|-----------------|------------------------|------------|--------|--|

| 分辨率             | $ m R_{AIN}~(k\Omega)$ | 快速通道       | 慢速通道   |  |

|                 | 0.14                   | 45.0       | 73.0   |  |

|                 | 0.6                    | 79.0       | 103.0  |  |

| 12-bit          | 4.6                    | 300.0      | 345.0  |  |

| 12 <b>-</b> 01t | 9.5                    | 576.0      | 651.0  |  |

|                 | 19                     | 1131.0     | 1257.0 |  |

|                 | 48                     | 2776.0     | 3051.0 |  |

| 10-bit          | 0.14                   | 39.0       | 61.0   |  |

地址:深圳市南山区高新北区宝深路109号国民技术大厦 电话: +86-755-86309900 传真: +86-755-86169100

|       | 0.6  | 64.0   | 88.0   |

|-------|------|--------|--------|

|       | 4.6  | 250.0  | 357.0  |

|       | 9.5  | 478.0  | 540.0  |

|       | 19   | 935.0  | 1040.0 |

|       | 48   | 2294.0 | 2526.0 |

|       | 0.14 | 33.0   | 50.0   |

|       | 0.6  | 52.0   | 71.0   |

| 0.1.4 | 4.6  | 202.0  | 234.0  |

| 8-bit | 9.5  | 391.0  | 457.0  |

|       | 19   | 800.0  | 1012.0 |

|       | 48   | 1838.0 | 2027.0 |

|       | 0.14 | 27.0   | 40.0   |

|       | 0.6  | 41.0   | 56.0   |

| 6-bit | 4.6  | 153.0  | 177.0  |

| 0-011 | 9.5  | 292.0  | 330.0  |

|       | 19   | 569.0  | 642.0  |

|       | 48   | 1435.0 | 1666.0 |

图 1-4 ADC 采样时间表

注:采样时间需根据输入时钟和ADC寄存器可选的采样周期综合配置,原则上ADC采样周期配置应大于等于表中最小采样周期数。

### 1.8 PGA 应用参考

N32H47X 系列芯片内包含 4 个灵活的可编程增益放大器 (PGA), 详见对应数据手册的引脚复用定义。任意一个差分 PGA 可拆分为两个单端 PGA 独立使用。

注: N32H48X 系列芯片不支持 PGA。

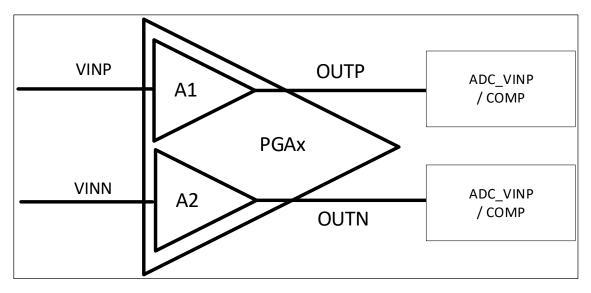

### 1.8.1 单端模式应用

PGA 的单端模式应用如下图所示:

图 1-5 PGA 单端工作结构

此时一个 PGA 将拆分为两个独立的放大器,每一端输入对应单独的输出:

$OUTP = A1 \times VINP$

$OUTN = A2 \times VINN$

两个放大器的放大增益 A1/A2 通过不同的寄存器单独配置。此时 PGA 的输出可接到比较器工作或者接到 ADC 的正端输入进行测量。

PGA 的输入可以来自于外部硬件配置或内部 DAC 输出,通过寄存器选择特定输入通道。图 1-4 中左半部分虚线框内为一种硬件配置实例:

通过电流源 C1/C2 与 Rsense 采集需要放大的小信号电压。通过共模 Rcm 拉升到合适的适合放大的电压,再进入 PGA 进行放大。

注意要求阻值 Rcm >> Rsense.

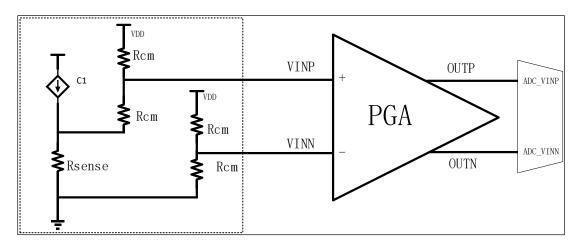

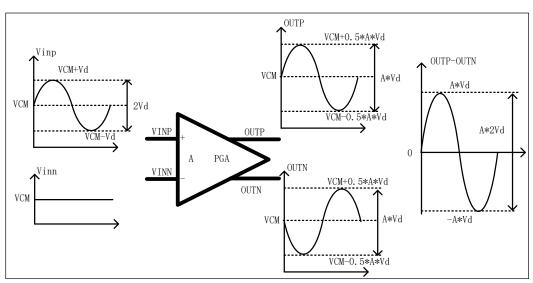

### 1.8.2 差分模式应用

大多数情况下,由于输入噪声以及电路寄生参数的原因,使用单端模式会产生较大的误差,此时使用差分模式工作能够有效的提高输出精度。其工作模式如下图:

图 1-6 PGA 差分工作结构

差分模式下,两端的输入将通过 PGA 进行差分放大:

$$Voutp = Vinn + 1/2 \times A \times (Vinp-Vinn)$$

Voutn= Vinn -  $1/2 \times A \times (Vinp-Vinn)$

差分输出的增益 A 由单独的寄存器配置,放大的差分信号同时进入 ADC 的正负端进行测量。

PGA 的输入可以来自于外部硬件配置或内部 DAC 输出,通过寄存器选择特定输入通道。图 1-5 中虚线框内为一种硬件配置实例:

通过电流源 C1 与 Rsense 采集需要放大的小信号电压。通过共模 Rcm 电阻分压提供共模电压,进入 PGA 进行差分放大:

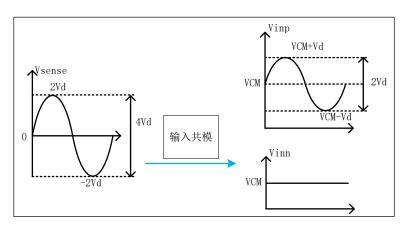

图 1-7 PGA 差分输入波形

设计要求阻值 Rcm >> Rsense,设 Vsense 产生摆幅为 4Vd 的正弦波电压。两端通过 VDD 分压电路分别 抬高 VCM, 一般 VCM=VDD/2, 此时 VINN 为 VCM 固定电压值, VINN 成为了共模电压 VCM, 摆幅 为 Vd 的正弦波电压。抬高后的电压成为 PGA 的正负两端输入。

提供的共模电压 VCM 是必要的,因为 PGA 两端放大后的输出要确保远离最大摆幅或者最小摆幅,否则会造成较大的精度损失。

信号进入 PGA 放大后由 OUTP/OUTN 两端输出,配置 PGA 差分增益为 A,两端输入信号放大后如图 所示:

图 1-8 PGA 差分放大输出波形

差分输出与输入由公式:

$Voutp = Vinn + 1/2 \times A \times (Vinp-Vinn)$

Voutn= Vinn -  $1/2 \times A \times (Vinp-Vinn)$

计算。可以看到:

OUTP 输出为共模电压不变, PN 差分输入正向放大 0.5×A 倍

OUTN 输出为共模电压不变, PN 差分输入负向放大 0.5×A 倍

最后进入 ADC 的信号为共模消除摆幅为 A×2Vd 的信号,摆幅相较输入 2Vd 增大了 A 倍。

同时 VCM 保证了两端输出不接近电源与地,不会造成信号失真。

#### 1.8.3 PGA 使用注意事项

为确保 PGA 正常工作以及精确度,使用时要注意以下几点:

1. 为防止输出失真单端/差分模式下输入范围要基于增益与理论输出电压考虑:

单端模式下确保: 0.3V < A×Vin < VDDA-0.3V

差分模式下,每一端的输出电压 Vout 要确保 0.3V < OUTP/N < VDDA-0.3V,

2. 差分模式必须给 N 端提供合适的共模电压 VCM, 通常 VCM=VDDA/2.

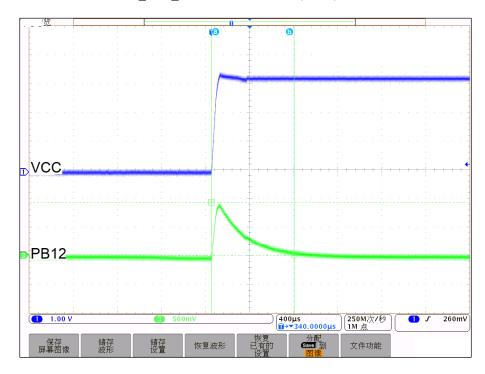

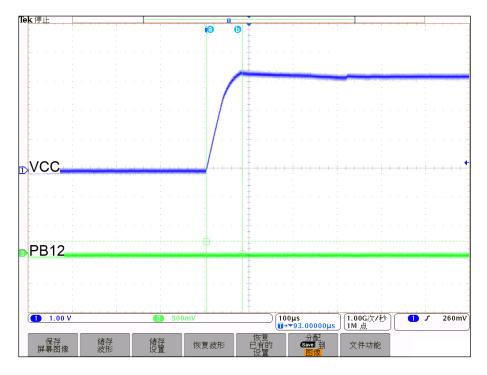

#### 1.9 IO 上电脉冲处理

上电过程中由于 IO 处于高阻态及内部电路耦合特性,上电瞬间会引起 IO 上出现高电平脉冲(实际的高脉冲电压值请用户实测)。若该脉冲会影响其应用,建议在对应 IO 上挂适当电容(1nF~100nF)或外加适当下拉电阻(10K~100K)处理。

下图为开发板 N32H473CEU7 STB V1.0 上电过程中 IO(PB12)波形图:

图 1-9 上电过程 IO(PB12)波形

下图为开发板 N32H473CEU7 STB V1.0 上电过程中 IO(PB12)外加 10K 下拉电阻后的波形图:

图 1-10 上电过程 IO (PB12) 外加下拉电阻处理后波形

### 1.10 IO 耐压值

芯片使用时请注意各 IO 耐压值,在数据手册引脚复用定义的 I/O 结构一栏,标注了 FT: 5V tolerant IO, 这类型 IO 在与外部其它不同电压域的 IO 进行通讯时,需要做电平转换。

| 封装。    |             |                         |        | ę.          |         |         |             | ÷      | ξ <b>j</b> (2) | F "                                   |         | 可选的复用功能。                                                                 |             |

|--------|-------------|-------------------------|--------|-------------|---------|---------|-------------|--------|----------------|---------------------------------------|---------|--------------------------------------------------------------------------|-------------|

| UQFN32 | UQFN48      | LQFP48                  | LQFP64 | LQFP80.     | LQFP100 | LQFP128 | 管脚名称。       | 类型(1)。 | 班              | Fail-<br>safe <sup>(3)</sup> 。<br>支持。 | (3) 王切能 | 默认↩                                                                      | 重定义↩        |

| -0     | -47         | <b>-</b> 4 <sup>7</sup> | -4-    | <b>-</b> 47 | 1₽      | 1₽      | PE2. Shulli | I/O4   | FT₽            | Yes₽                                  | PE2.    | TRACECLK+ GTIM2_CH1+ SPI4_SCK+ ATIM3_CH1+ USART4_TX+ FEMC_A23+ EVENTOUT- | <b>-</b> e) |

| -4     | <b>-</b> \$ | -47                     | -47    | <b>-</b> 4  | 2₽      | 2.0     | РЕ3₽        | I/O∻   | FT₽            | Yes                                   | PE3÷    | TRACED0+ GTIM2_CH2+ SPI4_NSS+ ATIM3_CH2+ USART4_RX+ FEMC_A19+ EVENTOUT-  | <b>-</b> ¢) |

图 1-11 数据手册引脚复用定义的 I/O 结构

注: FT/FTa: 5V tolerant IO; TTa: 3.3V standard IO。在使用芯片时需注意 IO 的耐压值。

### 1.11 防静电设计

#### 1.11.1 PCB 设计

对于普通两层板的 PCB 设计,建议信号线周围做包地处理,PCB 板边也尽量做到铺地环绕。在成本允许的条件下,可以用四层板或多层板设计,在多层 PCB 中地线面作为一个重要的电荷源,可抵消静电放电源上的电荷,这有利于减小静电场带来的问题。PCB 地线面也可作为其对信号线的屏蔽体(当然,地线面的开口越大,其屏蔽效能就越低)。另外,如果发生放电,由于 PCB 板的地平面很大,电荷很容易注入到地线面中,而不是进入到信号线中。这样将有利于对元件进行保护,因为在引起元件损坏前,电荷可以泄放掉。

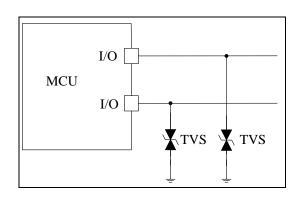

#### 1.11.2 ESD 防护器件

在实际产品设计中,芯片自身有一定的抗静电能力,N32H47X/N32H48X 系列 MCU ESD(HBM)模式下静电等级为+/-4KV,但如果有更高的 ESD 防护等级要求,且有芯片的管脚需要直接外接作为产品的输出或输入口,此时,芯片的管脚就直接暴露在产品的最外面,不能通过铺地等方式进行隔离。这种条件下,一般需要考虑外加 ESD 防护器件,TVS 管是一种典型的 ESD 保护器件,以下是典型的连接方式示例。

图 1-12 I/O 管脚上 TVS 连接方式

### 1.12 调试接口

N32H47X/N32H48X 系列芯片支持串行接口(SWD)和 JTAG 调试接口,详细应用请参考相关用户手册。

| 调试信号       | GPIO 引脚 |

|------------|---------|

| JTMS/SWDIO | PA13    |

| JTCK/SWCLK | PA14    |

| JTDI       | PA15    |

| JTDO       | PB3     |

| JNTRST     | PB4     |

表 1-1 调试接口

# 1.13 BOOT 串口接口

N32H47X/N32H48X 系列芯片支持 BOOT 串口通讯,串口接口如下表:

| BOOT 串口   | GPIO 引脚 |  |

|-----------|---------|--|

| USART1_TX | PA9     |  |

| USART1_RX | PA10    |  |

表 1-2 串口接口

### 2. 整体设计建议

#### 1) 印制电路板

建议使用有专门独立的接地层(VSS)和专门独立的供电层(VDD)的多层印制电路板,从而能提供好的耦合性能和屏蔽效果。在实际应用中,如考虑成本因素不能使用多层印制电路板,那么在设计电路时就需保证一个好的接地和供电的结构。

#### 2) 器件位置

在 PCB 设计时根据各器件对 EMI 影响的不同,需把不同的电路分开布局。比如,大电流电路、低电压电路、以及高频器件等。从而减少 PCB 上的交叉耦合。

#### 3) 接地和供电(VSS, VDD)

各模块(模拟电路、数字电路、敏感度低的电路)都应该单独接地,数字地和模拟地分开,所有的地最终都应在一个点上连到一起。根据印制线路板电流的大小,尽量加粗电源线宽度,减少环路电阻。同时,电源线、地线的走向和电流的方向应尽量一致,且电源应尽量靠近地线,减小回路的区域。这样有助于增强抗噪声能力。PCB上没有器件的区域,需要填充为地,以提供好的屏蔽效果。

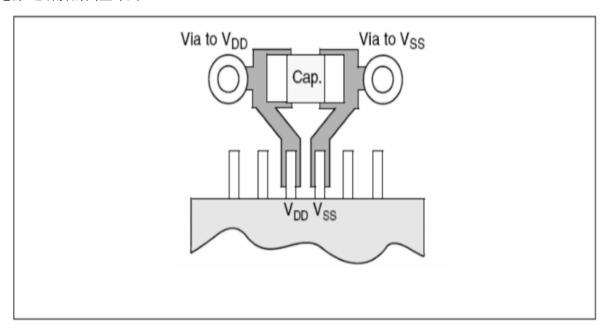

#### 4) 去耦合

所有的电源引脚都需要适当的连接到电源。这些连接,包括焊盘、连线和过孔应该具备尽量小的阻抗。通常采用增加连线宽度的办法,同时每对 VDD 与 VSS 引脚都必须在靠近芯片处放置去耦电容。下图为电源/地引脚的典型布局。

图 2-1 VDD/VSS 引脚的典型布局

## 3. 最小系统参考设计原理图

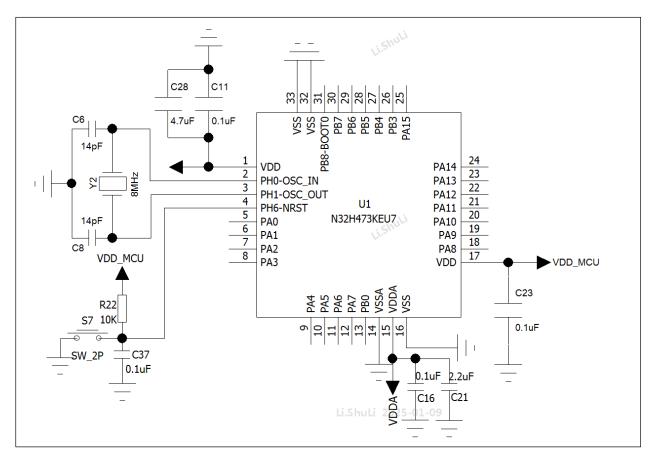

### 3.1 UQFN32-N32H473KEU7

图 3-1 UQFN32 封装最小系统参考设计原理图

地址: 深圳市南山区高新北区宝深路109号国民技术大厦 电话: +86-755-86309900 传真: +86-755-86169100

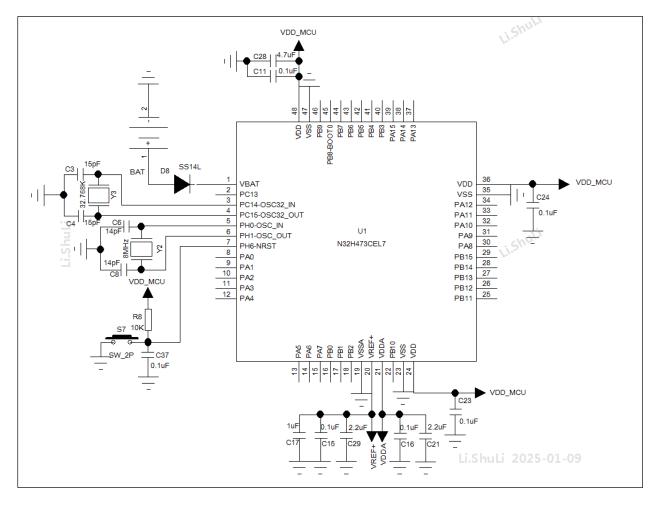

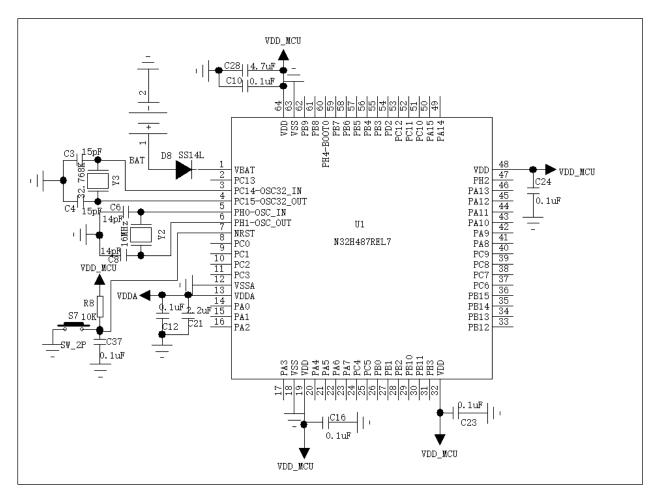

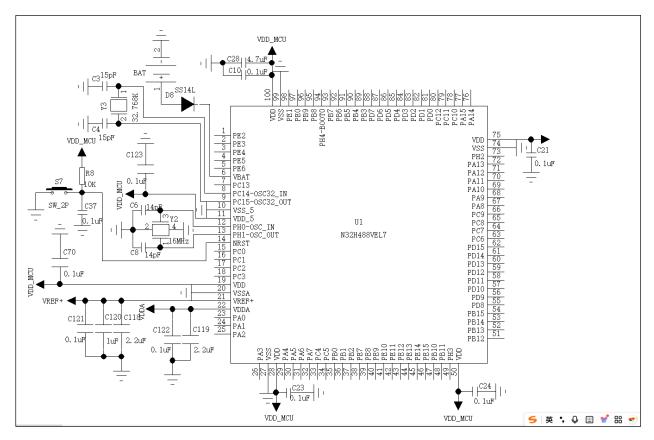

## 3.2 LQFP48-N32H473CEL7

图 3-2 LQFP48 封装最小系统参考设计原理图

地址: 深圳市南山区高新北区宝深路109号国民技术大厦 电话: +86-755-86309900 传真: +86-755-86169100

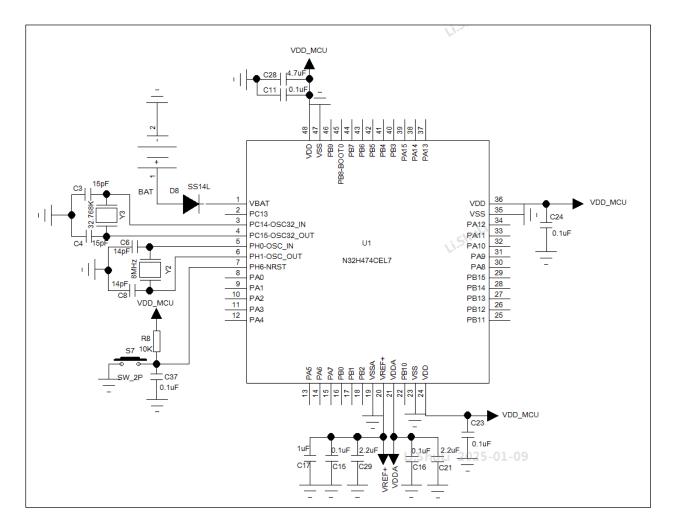

### 3.3 LQFP48-N32H474CEL7

图 3-3 LQFP48 封装最小系统参考设计原理图

地址: 深圳市南山区高新北区宝深路109号国民技术大厦 电话: +86-755-86309900 传真: +86-755-86169100

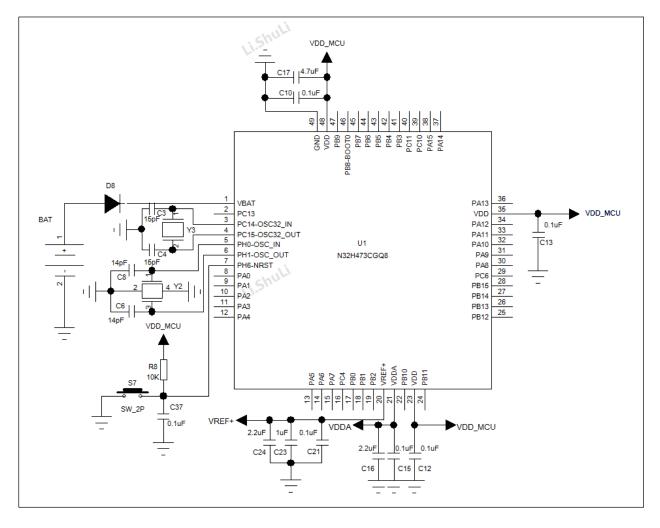

## 3.4 QFN48-N32H473CGQ8

图 3-4 QFN48 封装最小系统参考设计原理图

地址: 深圳市南山区高新北区宝深路109号国民技术大厦 电话: +86-755-86309900 传真: +86-755-86169100

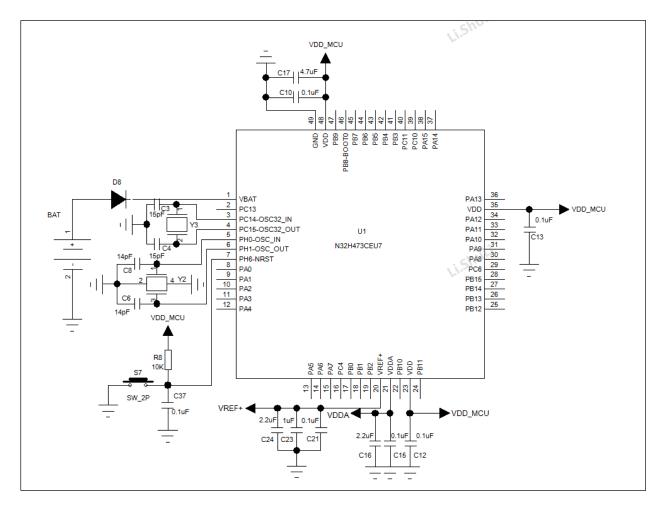

## 3.5 UQFN48-N32H473CEU7

图 3-5 UQFN48 封装最小系统参考设计原理图

地址: 深圳市南山区高新北区宝深路109号国民技术大厦 电话: +86-755-86309900 传真: +86-755-86169100

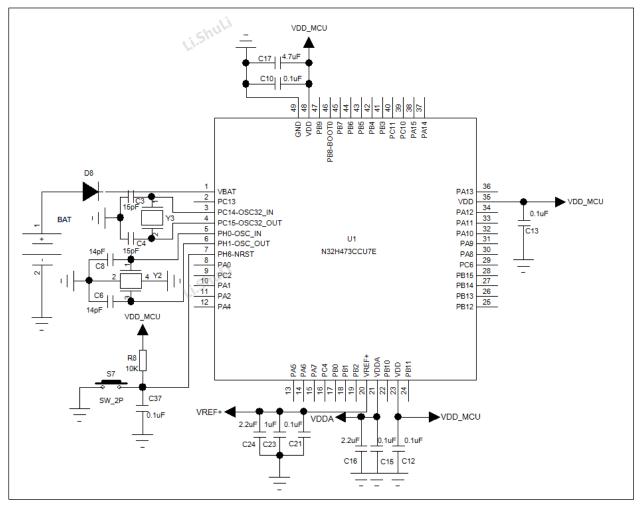

## 3.6 UQFN48-1-N32H473CCU7E

图 3-6 UQFN48-1 封装最小系统参考设计原理图

地址: 深圳市南山区高新北区宝深路109号国民技术大厦 电话: +86-755-86309900 传真: +86-755-86169100

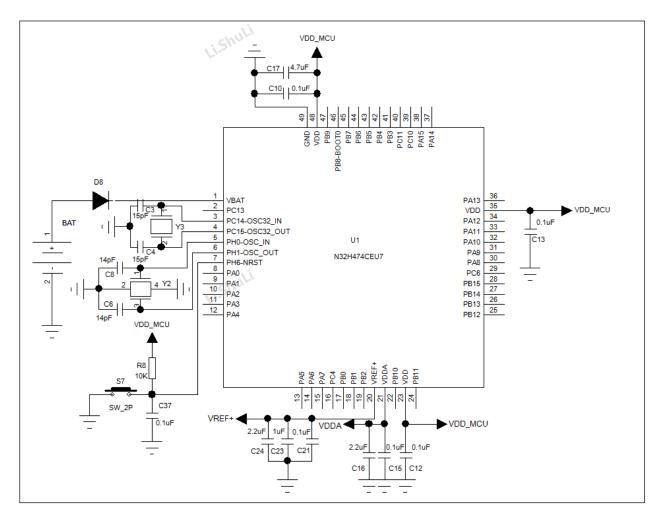

## 3.7 UQFN48-N32H474CEU7

图 3-7 UQFN48 封装最小系统参考设计原理图

地址: 深圳市南山区高新北区宝深路109号国民技术大厦 电话: +86-755-86309900 传真: +86-755-86169100

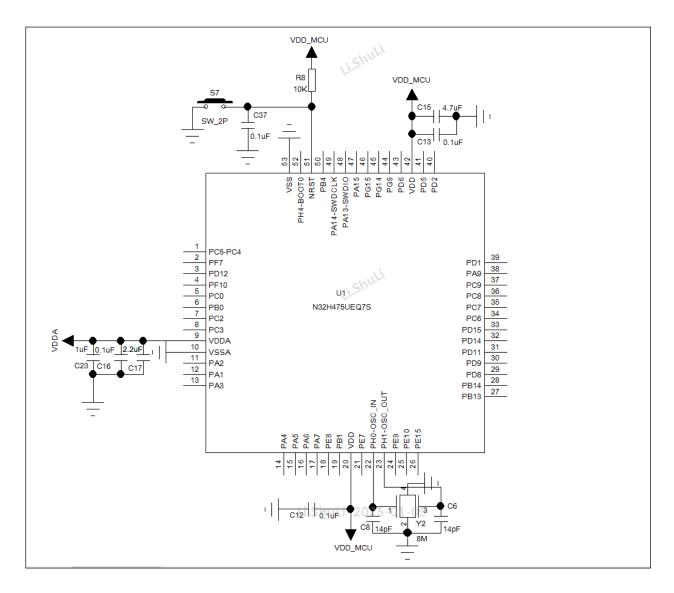

## 3.8 QFN52-N32H475UEQ7S

图 3-8 QFN52 封装最小系统参考设计原理图

地址: 深圳市南山区高新北区宝深路109号国民技术大厦 电话: +86-755-86309900 传真: +86-755-86169100

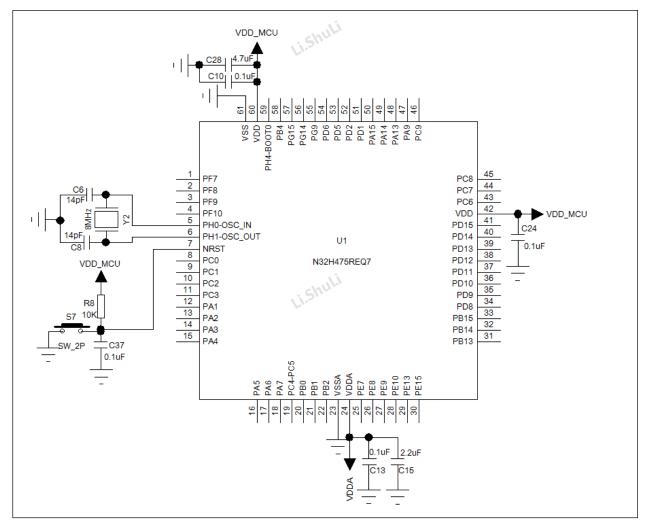

## 3.9 QFN60-N32H475REQ7

图 3-9 QFN60 封装最小系统参考设计原理图

地址: 深圳市南山区高新北区宝深路109号国民技术大厦 电话: +86-755-86309900 传真: +86-755-86169100

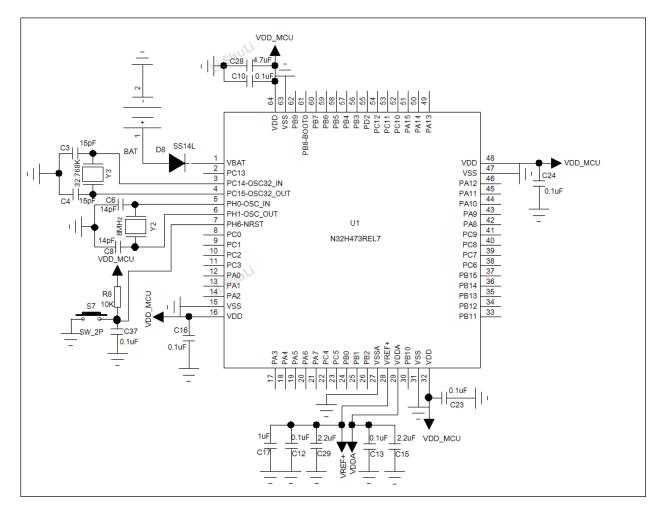

### 3.10 LQFP64-N32H473REL7

图 3-10 LQFP64 封装最小系统参考设计原理图

地址: 深圳市南山区高新北区宝深路109号国民技术大厦 电话: +86-755-86309900 传真: +86-755-86169100

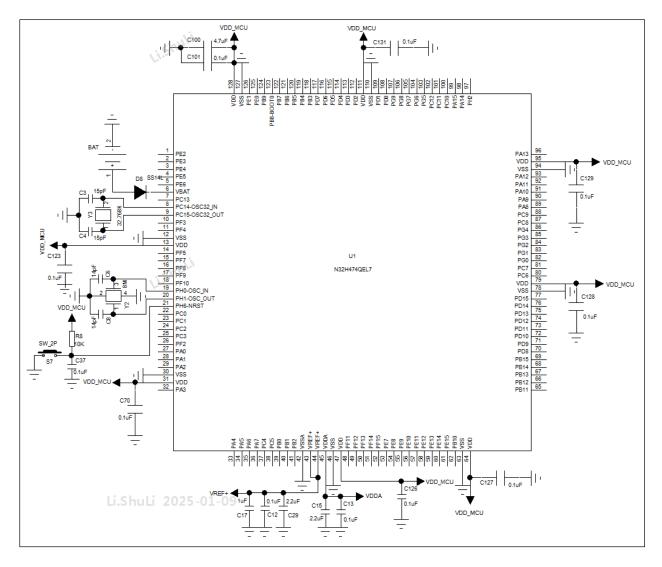

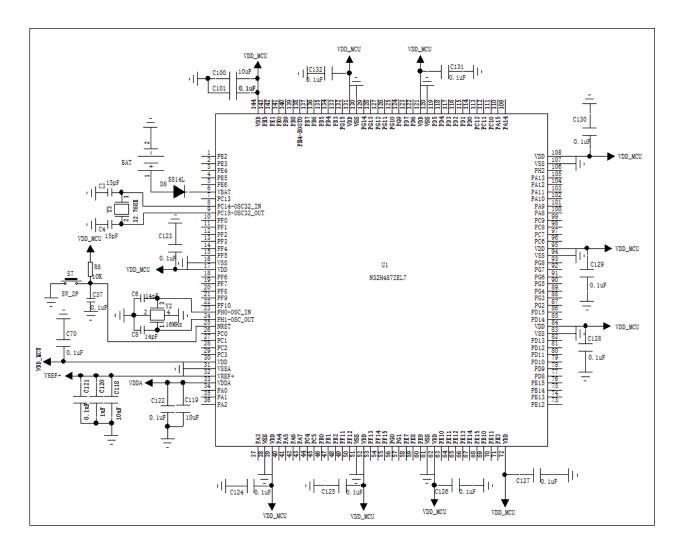

### 3.11 LQFP64-N32H474REL7

图 3-11 LQFP64 封装最小系统参考设计原理图

地址: 深圳市南山区高新北区宝深路109号国民技术大厦 电话: +86-755-86309900 传真: +86-755-86169100

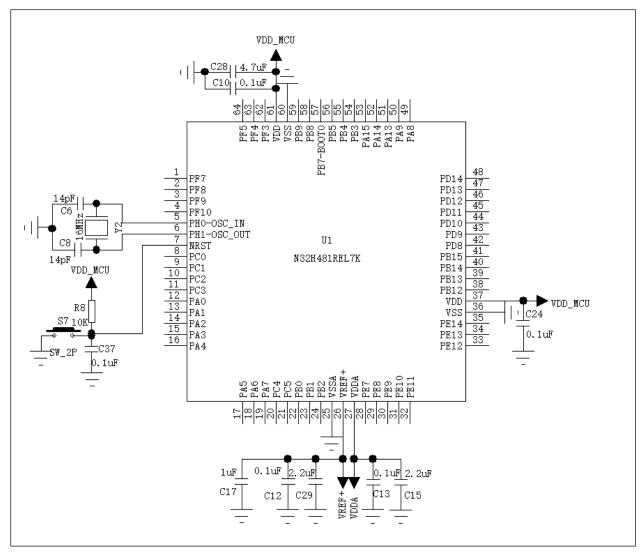

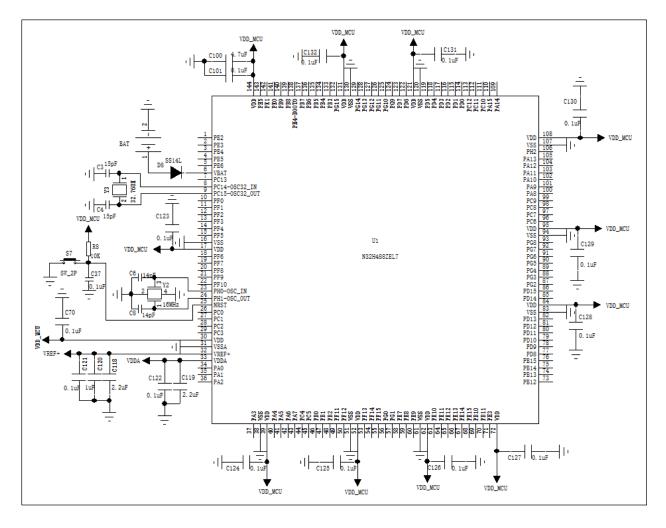

### 3.12 LQFP64-N32H481REL7K

图 3-12 LQFP64 封装最小系统参考设计原理图

地址: 深圳市南山区高新北区宝深路109号国民技术大厦 电话: +86-755-86309900 传真: +86-755-86169100

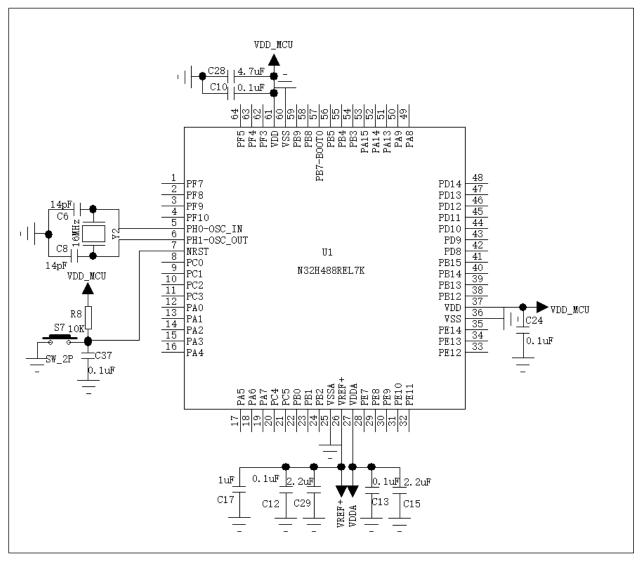

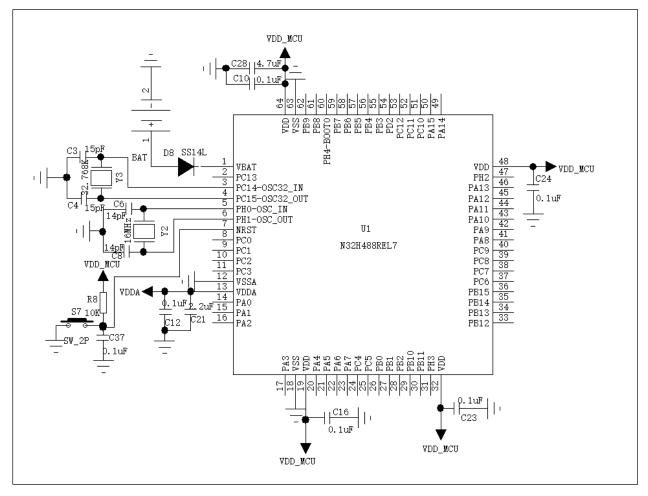

### 3.13 LQFP64-N32H488REL7K

图 3-13 LQFP64 封装最小系统参考设计原理图

地址: 深圳市南山区高新北区宝深路109号国民技术大厦 电话: +86-755-86309900 传真: +86-755-86169100

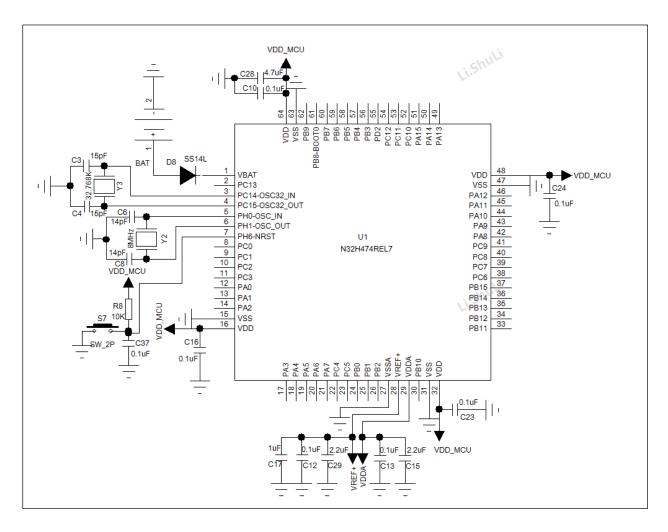

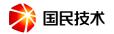

### 3.14 LQFP64-N32H482REL7

图 3-14 LQFP64 封装最小系统参考设计原理图

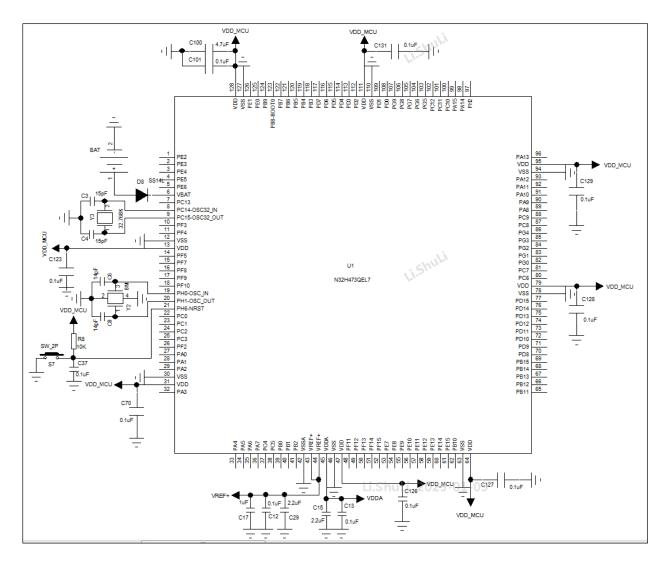

### 3.15 LQFP64-N32H487REL7

图 3-15 LQFP64 封装最小系统参考设计原理图

### 3.16 LQFP64-N32H488REL7

图 3-16 LQFP64 封装最小系统参考设计原理图

地址: 深圳市南山区高新北区宝深路109号国民技术大厦 电话: +86-755-86309900 传真: +86-755-86169100

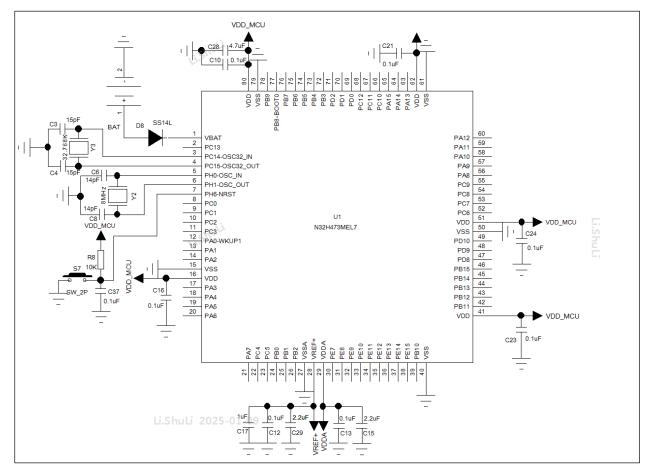

### 3.17 LQFP80-N32H473MEL7

图 3-17 LQFP80 封装最小系统参考设计原理图

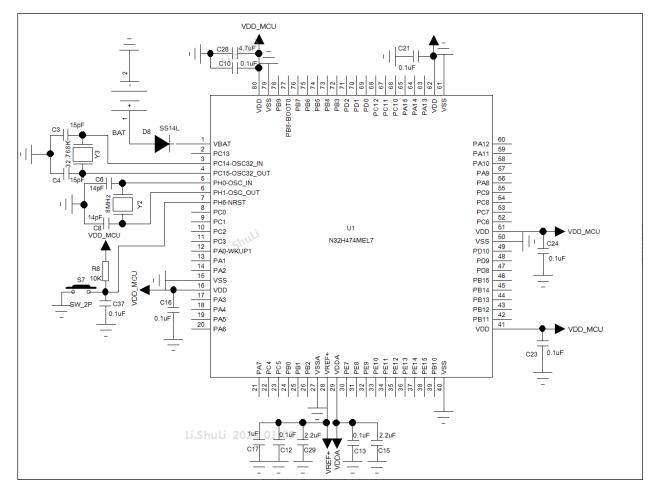

### 3.18 LQFP80-N32H474MEL7

图 3-18 LQFP80 封装最小系统参考设计原理图

### 3.19 LQFP100-N32H474VEL7

图 3-19 LQFP100 封装最小系统参考设计原理图

地址: 深圳市南山区高新北区宝深路109号国民技术大厦 电话: +86-755-86309900 传真: +86-755-86169100

### 3.20 LQFP100-N32H473VEL7

图 3-20 LQFP100 封装最小系统参考设计原理图

地址:深圳市南山区高新北区宝深路109号国民技术大厦 电话: +86-755-86309900 传真: +86-755-86169100

### 3.21 LQFP100-N32H482VEL7

图 3-21 LQFP100 封装最小系统参考设计原理图

### 3.22 LQFP100-N32H487VEL7

图 3-22 LQFP100 封装最小系统参考设计原理图

### 3.23 LQFP100-N32H488VEL7

图 3-23 LQFP100 封装最小系统参考设计原理图

地址: 深圳市南山区高新北区宝深路109号国民技术大厦 电话: +86-755-86309900 传真: +86-755-86169100

### 3.24 LQFP128-N32H474QEL7

图 3-24 LQFP128 封装最小系统参考设计原理图

地址: 深圳市南山区高新北区宝深路109号国民技术大厦 电话: +86-755-86309900 传真: +86-755-86169100

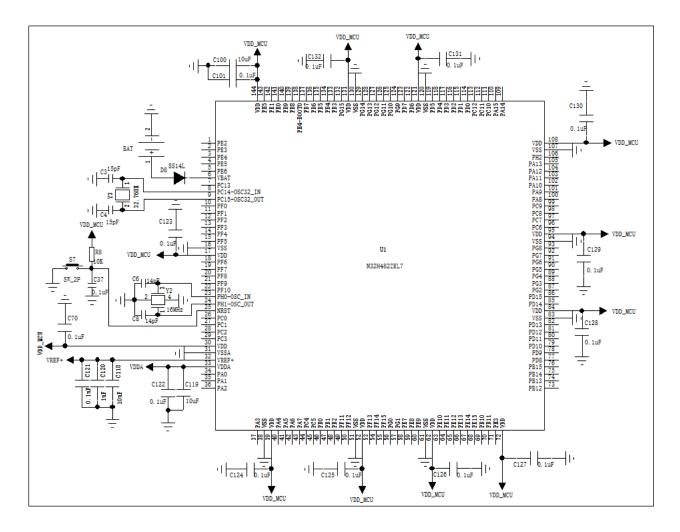

### 3.25 LQFP128-N32H473QEL7

图 3-25 LQFP128 封装最小系统参考设计原理图

地址: 深圳市南山区高新北区宝深路109号国民技术大厦 电话: +86-755-86309900 传真: +86-755-86169100

### 3.26 LQFP144-N32H482ZEL7

图 3-26 LQFP144 封装最小系统参考设计原理图

地址:深圳市南山区高新北区宝深路109号国民技术大厦 电话: +86-755-86309900 传真: +86-755-86169100

### 3.27 LQFP144-N32H487ZEL7

图 3-27 LQFP144 封装最小系统参考设计原理图

地址: 深圳市南山区高新北区宝深路109号国民技术大厦 电话: +86-755-86309900 传真: +86-755-86169100

### 3.28 LQFP144-N32H488ZEL7

图 3-28 LQFP144 封装最小系统参考设计原理图

以上是不同封装最小系统参考设计原理图,主要体现供电电源去耦电容、时钟、复位电路等设计;时钟电路和备用电池取决于用户设计;

芯片内部支持内部高速和低速时钟可供用户选择;

模拟电源 VDDA 建议由外部稳定电源供电,若直连 VDD 供电,需做相应滤波处理。

对于 N32H473/474/481/482/487/488 系列芯片:

当 VERF+使用内置参考源 VREFBUF 时, VREF+引脚建议就近放置一个 0.1uF 和一个 1uF 的电容, 当 VERF+由外部供电时, VREF+引脚建议就近放置一个 0.1uF 和一个 2.2uF 的电容。

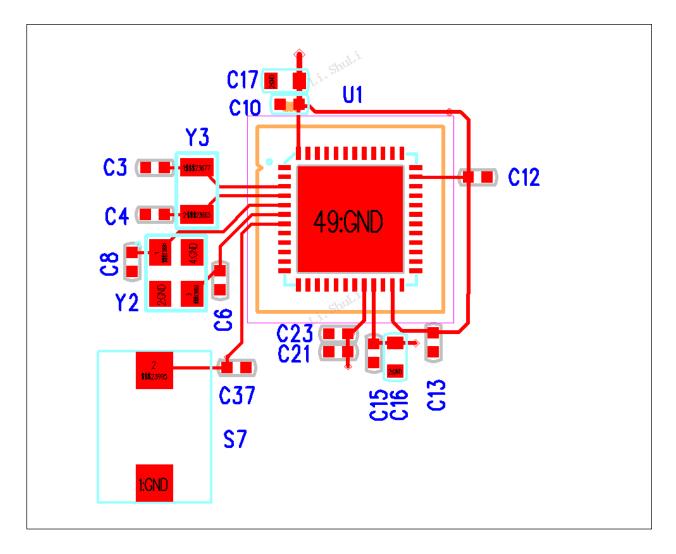

## 4. PCB LAYOUT 参考

图 4-1 UQFN48 封装 PCB LAYOUT 参考图

#### 注:

- 1、PCB LAYOUT 设计时,每一个电源管脚都需要就近放置去耦电容;

- 2、HSE 和 LSE 的外部晶体及走线尽可能在周围做包地处理,晶体下面一层靠近晶体的区域也需要铺地,不能有信号线穿过,防止信号线干扰晶体信号;

- 3、HSE 和 LSE 用作晶振时, 走线不宜过长, 避免天线效应。

地址: 深圳市南山区高新北区宝深路109号国民技术大厦 电话: +86-755-86309900 传真: +86-755-86169100

# 5. 历史版本

| 版本     | 日期         | 备注                                                                                                                                      |

|--------|------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| V0.7.0 | 2023-12-20 | 创建文档                                                                                                                                    |

| V0.8.0 | 2024-4-8   | <ol> <li>添加不同封装最小系统设计原理图</li> <li>添加 PGA 应用参考</li> <li>增加 ADC 采样时间表</li> </ol>                                                          |

| V1.0.0 | 2024-11-18 | 1. 更新 N32H473CGQ8/ N32H473CCU7E/ N32H481REL7K/ N32H475UEQ7S/ N32H475REQ7/ N32H488REL7K/ N32H488REL7/ N32H488VEL7/ N32H488ZEL7 最小系统设计原理图 |

| V1.1.0 | 2025-5-12  | 1. 修改 N32H48x 系列最小系统设计原理图 HSE 为 16M                                                                                                     |

### 6. 声明

国民技术股份有限公司(下称"国民技术")对此文档拥有专属产权。依据中华人民共和国的法律、条约以及世界其他法域相适用的管辖,此文档及其中描述的国民技术产品(下称"产品")为公司所有。

国民技术在此并未授予专利权、著作权、商标权或其他任何知识产权许可。所提到或引用的第三方名称或品牌(如有)仅用作区别之目的。

国民技术保留随时变更、订正、增强、修改和改良此文档的权利,恕不另行通知。请使用人在下单购买前联系国民技术获取此文档的最新版本。

国民技术竭力提供准确可信的资讯,但即便如此,并不推定国民技术对此文档准确性和可靠性承担责任。使用此文档信息以及生成产品时,使用者应当进行合理的设计、编程并测试其功能性和安全性,国民技术不对任何因使用此文档或本产品而产生的任何直接、间接、意外、特殊、惩罚性或衍生性损害结果承担责任。

国民技术对于产品在系统或设备中的应用效果没有任何故意或保证,如有任何应用在其发生操作不当或故障情况下,有可能致使人员伤亡、人身伤害或严重财产损失,则此类应用被视为"不安全使用"。

不安全使用包括但不限于:外科手术设备、原子能控制仪器、飞机或宇宙飞船仪器、所有类型的安全装置以及其他旨在支持或维持生命的应用。

所有不安全使用的风险应由使用人承担,同时使用人应使国民技术免于因为这类不安全使用而导致被 诉、支付费用、发生损害或承担责任时的赔偿。

对于此文档和产品的任何明示、默示之保证,包括但不限于适销性、特定用途适用性和不侵权的保证责任,国民技术可在法律允许范围内进行免责。

未经明确许可,任何人不得以任何理由对此文档的全部或部分进行使用、复制、修改、抄录和传播。