# N32H76X/N32H78X系列硬件设计指南

简介

本文档详细介绍 N32H76X/N32H78X 系列 MCU 硬件设计检查列表,以 便为用户提供硬件设计指导。

国民技术 版权所有

# 目录

| 1. | N32H76X/N32H78X 系列 MCU 硬件设计检查列表1 |                              |    |  |  |  |

|----|----------------------------------|------------------------------|----|--|--|--|

|    | 1.1                              | 电源供电简介                       | 1  |  |  |  |

|    | 1.2                              | 供电方案                         | 2  |  |  |  |

|    | 1.2.1                            | 1 N32H765/H78X 系列芯片 VCAP 供电: | 6  |  |  |  |

|    | 1.2.2                            | 2 N32H760/H762 系列芯片 VCAP 供电: | 8  |  |  |  |

|    | 1.3                              | 备用电池                         | 9  |  |  |  |

|    | 1.4                              | 外部引脚复位电路                     | 9  |  |  |  |

|    | 1.5                              | 外部时钟电路                       | 9  |  |  |  |

|    | 1.6                              | 启动引脚连接                       | 9  |  |  |  |

|    | 1.7                              | ADC 转换器                      | 10 |  |  |  |

|    | 1.8                              | 高速通信接口设计建议                   | 12 |  |  |  |

|    | 1.8.1                            | 1 USBHS 接口                   | 12 |  |  |  |

|    | 1.8.2                            | 2 MIPI 接口                    | 12 |  |  |  |

|    | 1.8.3                            | 3 EtherCAT /ETH 接口           | 12 |  |  |  |

|    | 1.8.4                            | 4 SDRAM 接口                   | 13 |  |  |  |

|    | 1.9                              | IO 上电脉冲处理                    | 14 |  |  |  |

|    | 1.10                             | IO 耐压值                       | 15 |  |  |  |

|    | 1.11                             | 防静电设计                        | 15 |  |  |  |

|    | 1.11                             | .1 PCB 设计                    | 15 |  |  |  |

|    | 1.11                             | .2 ESD 防护器件                  | 15 |  |  |  |

|    | 1.12                             | 调试接口                         | 16 |  |  |  |

|    | 1.13                             | BOOT 串口接口                    | 16 |  |  |  |

|    | 1.14                             | 各模块设计注意事项                    | 16 |  |  |  |

|    | 1.14                             | I.1 SDRAM                    | 16 |  |  |  |

|    | 1.14                             | I.2 SDMMC                    | 16 |  |  |  |

|    | 1.14                             | USBHS                        | 17 |  |  |  |

|    | 1.14                             | I.4 VREFBUF                  | 17 |  |  |  |

| 2. | 整体设计                             | ·<br>一建议                     | 18 |  |  |  |

| 3. | PCB LAY                          | YOUT 参考                      | 19 |  |  |  |

| 1. | 历史版本                             | <u> </u>                     | 20 |  |  |  |

| 5. | 声 明                              |                              | 21 |  |  |  |

# 1. N32H76X/N32H78X 系列 MCU 硬件设计检查列表

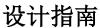

### 1.1 电源供电简介

N32H76X/N32H78X 系列芯片工作电压(VDD)为 2.3V~3.63V。主要外部电源有: VDD、VDD33\_USB、VCAP、VDDA、VREF、VBAT 引脚。其中 VDD 是芯片电源,主要给供电系统、时钟系统和 IO 供电; VDDA 为模拟外设电源,主要给模拟外设供电; VDD33\_USB 是 USB 专用供电电源; VCAP 是芯片核心供电电源; VREF 给模拟外设提供参考电源,以提供更高的精度; VBAT 连接电池,为备份域提供电源。电源引脚详细描述请参考芯片相关手册。

# 1.2 供电方案

图 1-1 供电方案

地址: 深圳市南山区高新北区宝深路109号国民技术大厦 电话: +86-755-86309900 传真: +86-755-86169100

图 1-1 供电方案中 10μF 电容须连接到指定 VDD 引脚, 各型号芯片具体指定 VDD 引脚请见下表:

| 型号    | 封装          | VDD                                          | VCAP                                                            |

|-------|-------------|----------------------------------------------|-----------------------------------------------------------------|

|       | TFBGA100    | VDD管脚上放置0.1uF                                | 接近芯片端先放置一个22uF+0.1uF,靠近每个VCAP管脚上放置0.1uF                         |

| H760  | LQFP100     | pin27和pin75放置10uF+0.1uF,其余VDD管<br>脚上放置0.1uF  | pin48和pin73放置10uF+0.1uF                                         |

|       | LQFP144     | pin39和pin108放置10uF+0.1uF,其余VDD管脚上放置0.1uF     | pin71和pin106放置10uF+0.1uF                                        |

|       | LQFP176     | pin49和pin127放置10uF+0.1uF,其余VDD管<br>脚上放置0.1uF | pin81和pin125放置10uF+0.1uF                                        |

| H762  | UFBGA176+25 | 接近芯片端先放置一个10uF+0.1uF,靠近每个VDD管脚上放置0.1uF       | 接近芯片端先放置一个22uF+0.1uF,靠近每个VCAP管脚上放置0.1uF                         |

| 11702 | LQFP208     | pin32和pin150放置10uF+0.1uF,其余VDD管脚上放置0.1uF     | pin92和pin148放置10uF+0.1uF                                        |

|       | UFBGA240+25 | 接近芯片端先放置一个10uF+0.1uF,靠近每个VDD管脚上放置0.1uF       | 接近芯片端先放置一个22uF+0.1uF,靠近每个VCAP管脚上放置0.1uF                         |

|       | LQFP144     | pin42和pin106放置10uF+0.1uF,其余VDD管脚上放置0.1uF     | 除了在输出电感位置放置10uF+0.1uF,另外在pin68、<br>pin105和pin140分别放置10uF+0.1uF  |

| H765  | UFBGA144    | 接近芯片端先放置10uF+0.1uF,靠近每个<br>VDD管脚上放置0.1uF     | 接近芯片端先放置一个22uF+0.1uF,靠近每个VCAP管脚上放置0.1uF                         |

| 11703 | LQFP176     | pin48和pin136放置10uF+0.1uF,其余VDD管脚上放置0.1uF     | 除了在输出电感位置放置10uF+0.1uF, 另外在pin80、<br>pin133和pin172分别放置10uF+0.1uF |

|       | UFBGA176+25 | 接近芯片端先放置10uF+0.1uF,靠近每个<br>VDD管脚上放置0.1uF     | 在输出电感位置放置47uF+0.1uF                                             |

|       | LQFP176     | pin48和pin136放置10uF+0.1uF,其余VDD管脚上放置0.1uF     | 除了在输出电感位置放置10uF+0.1uF, 另外在pin80、<br>pin133和pin172分别放置10uF+0.1uF |

| H785  | UFBGA176+25 | 接近芯片端先放置10uF+0.1uF,靠近每个<br>VDD管脚上放置0.1uF     | 在输出电感位置放置47uF+0.1uF                                             |

|       | LQFP208     | pin56和pin155放置10uF+0.1uF,其余VDD管<br>脚上放置0.1uF | 除了在输出电感位置放置10uF+0.1uF,另外在pin89、<br>pin152和pin199分别放置10uF+0.1uF  |

|       | TFBGA240+25 | 接近芯片端先放置10uF+0.1uF,靠近每个<br>VDD管脚上放置0.1uF     | 在输出电感位置放置47uF+0.1uF                                             |

|       | LQFP176     | pin48和pin136放置10uF+0.1uF,其余VDD管脚上放置0.1uF     | 除了在输出电感位置放置10uF+0.1uF, 另外在pin80、<br>pin133和pin172分别放置10uF+0.1uF |

| H787  | UFBGA169    | 接近芯片端先放置10uF+0.1uF,靠近每个<br>VDD管脚上放置0.1uF     | 在输出电感位置仿置47uF+0.1uF                                             |

|       | LQFP208     | pin56和pin155放置10uF+0.1uF,其余VDD管<br>脚上放置0.1uF | 除了在输出电感位置放置10uF+0.1uF,另外在pin89、<br>pin152和pin199分别放置10uF+0.1uF  |

|       | TFBGA240+25 | 接近芯片端先放置10uF+0.1uF,靠近每个<br>VDD管脚上放置0.1uF     | 在输出电感位置放置47uF+0.1uF                                             |

| H788  | UFBGA176+25 | 接近芯片端先放置10uF+0.1uF,靠近每个<br>VDD管脚上放置0.1uF     | 在输出电感位置放置47uF+0.1uF                                             |

表 1-1 各封装电源去耦电容设计参考

- 4个电源区域,通过外部电源给不同电源区域供电:

- VDD 域: 电压范围为 2.3V~3.63V, 主要为大部分 GPIO、HSE、 HSI、 PLL、POR/PDR、 BOR、 PVD 供电。

- VDD33 USB 域: 电压范围为 1.8V~3.6V,专门为 USB PHY 供电。

- VDDA 域: 电压范围为 2.3V~3.63V, 主要为 ADC, DAC, COMP、VREFBUF、TS 等供电。

- VCAP 域: 电压范围为 0.9V~0.99V (包含电源纹波), 主要为 CPU、AHB、APB、SRAM、FLASH、RCC、TRNG 和大部分外设供电

注意: VCAP 外部 LDO 供电,下电时,需要保证 VDD 先下电到 1V 以下,VCAP 再下电;为保证 VDD 和 VCAP 下电时序,VCAP 外部 LDO 供电时,供电模式推荐如下:

#### LDO 选型要求: 0.9V/1A(@25℃)

- 输入电压在 1.45V 时, 仍能输出 0.9V, 电流至少 200mA

- 在高温 105 °C@3.6V 时, 电流至少输出 1A

- 推荐型号: RT2516GSP

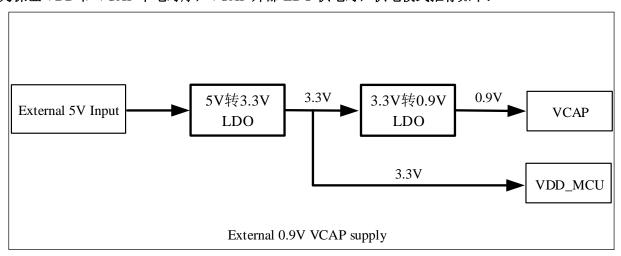

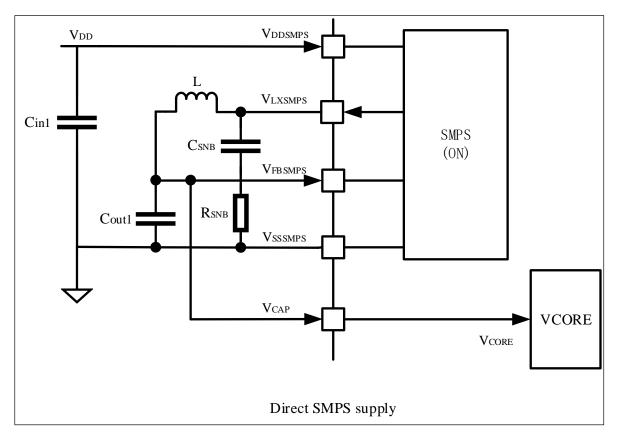

#### VCAP 内部 DCDC 供电,推荐电路如下:

注:图中输入输出电容温度系数推荐 X7R 类型。

VDD 为 MCU 主电源,必须由稳定的外部电源供电。电压范围 2.3V~3.63V,所有 VDD 引脚都需就近放置一颗 0.1uF 去耦电容,其中指定的 VDD 管脚还需增加一颗 10uF 去耦电容,具体指定 VDD 引脚请参考表 1-1《各封装电源去耦电容设计参考》。

VDDA 为模拟电源, VDDA 输入管脚建议就近放置一个 0.1uF 和一个 10uF 的电容。

VREF+为参考电压,为 ADC、DAC 提供参考电平,当 VERF+使用内置参考源 VREFBUF 时,VREF+引脚建议就近放置一个 0.1uF 和一个 1uF 的电容。当 VERF+由外部供电时,VREF+引脚建议就近放置一个 0.1uF 和一个 10uF 的电容。

VBAT 引脚主要给备电域(RTC、IWDG、Backup SRAM)供电,在主电源(VDD)关闭时,电源切换器可以将备份域的电源切换到 VBAT 引脚,使得备电域模块仍能正常运行。

VCAP 为芯片核心供电电源:

### 1.2.1 N32H765/H78X 系列芯片 VCAP 供电:

(1) 芯片内部 DCDC 为 VCAP 供电:

图 1-2 VCAP 由内部 DCDC 供电

#### 注:

- 1、L 电感量:2.2μH,饱和电流:1.2A。

- 2、C<sub>SNB</sub> 和 R<sub>SNB</sub> 为可选的阻容缓冲电路,可减少开关振铃,抑制 EMI.

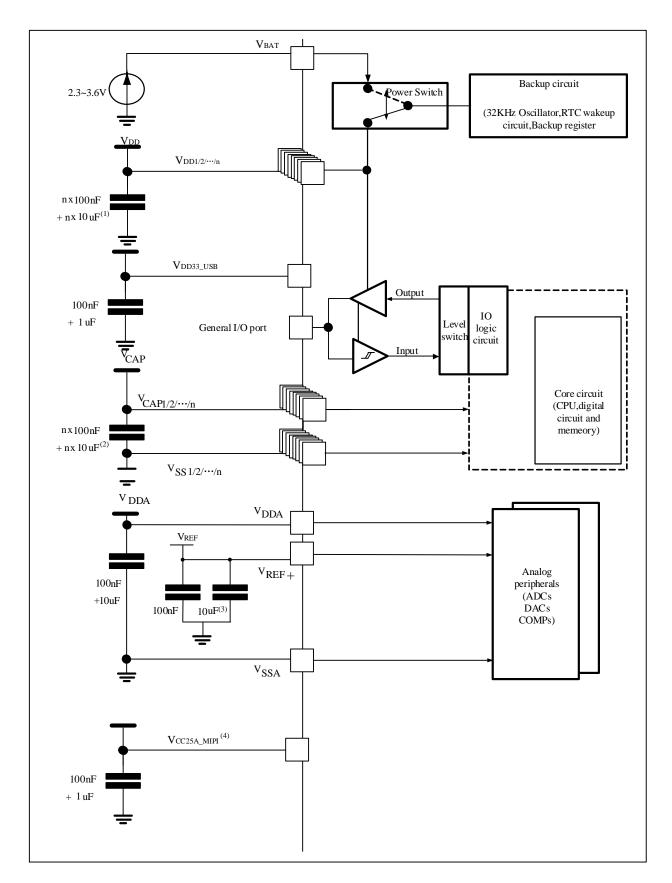

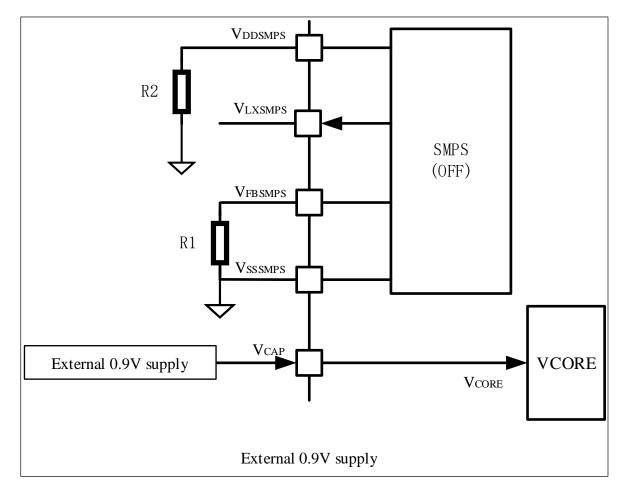

(2) 芯片外部 0.9V 为 VCAP 供电:

图 1-3 VCAP 由外部 LDO 供电

#### 注:

- 1、 当不使用 DCDC 供电模式时,VDDSMPS 和 VFBSMPS 管脚需接 0  $\Omega$  电阻下拉到地,防止漏电。

- 2、对于使用外部电源给 VCAP 供电的情况,要求外部电源能满足输入电压在 1.6V 及其以上时能稳定输出 0.9V, VCAP 供电电压范围为 0.9V~0.99V(包含电源纹波)。

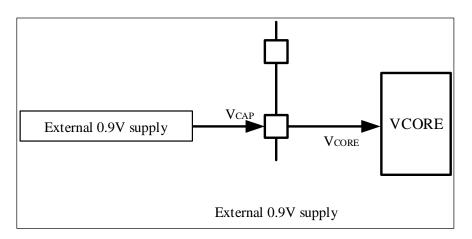

### 1.2.2 N32H760/H762 系列芯片 VCAP 供电:

(1) 芯片外部 0.9V 为 VCAP 供电

图 1-4 VCAP 由外部电源供电

#### 注:

1、对于使用外部电源给 VCAP 供电的情况,要求外部电源能满足输入电压在 1.6V 及其以上时能稳定输出 0.9V, VCAP 供电电压范围为 0.9V~0.99V(包含电源纹波)。

### 1.3 备用电池

VBAT 引脚主要给备电域(RTC、IWDG、Backup SRAM)供电,使得备电域模块在主电源(VDD)关闭时仍能正常运行。如果应用中没有外部电池,VBAT 必须在外部连接到 VDD。

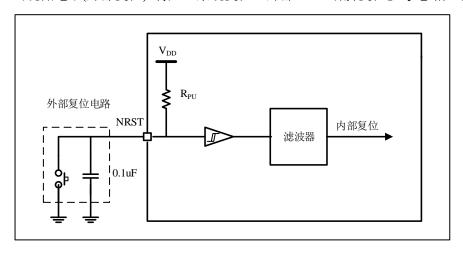

### 1.4 外部引脚复位电路

当NRST引脚上出现低电平(外部复位)将产生系统复位。外部NRST引脚复位参考电路如下。

图 1-5 系统复位图

注:复位引脚NRST在设计时建议不悬空,外挂电容0.1uF作为典型参考值给出,若需加快复位时间,NRST引脚可外加上拉,另外用户可根据产品实际需要决定是否增加复位按键。

### 1.5 外部时钟电路

N32H76X/N32H78X 系列 MCU 包含 2 个外部时钟: 外部高速时钟 HSE (4MHz~48MHz) 和外部低速时钟 LSE (通常使用 32.768KHz)。

HSE 和 LSE 根据晶振特性配置相应的负载电容,详细请参考相关数据手册中外部时钟特性描述。

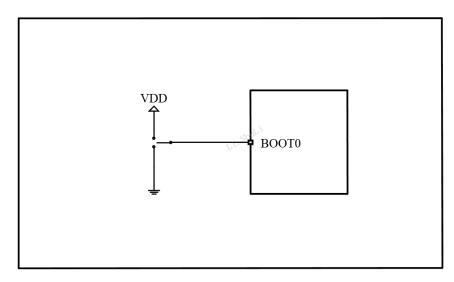

### 1.6 启动引脚连接

下图显示了 N32H76X/N32H78X 系列芯片选择启动存储器时所需的外部连接。关于启动模式请参考用户手册相关章节。

图 1-6 启动模式实现实例

BOOT引脚拉高,芯片复位后从BOOT区启动;BOOT引脚拉低,芯片复位后从用户区启动。启动模式请参考软件开发指南BOOT配置章节.

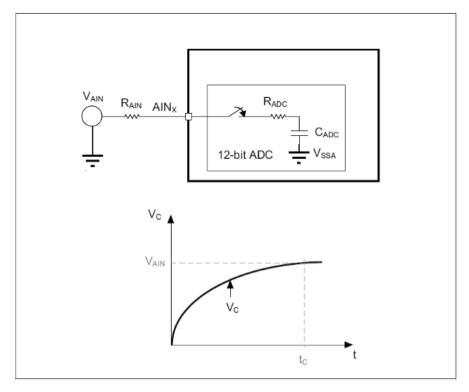

### 1.7 ADC 转换器

关于 ADC 电路设计,请注意如下几点:

- 1) 在使用 ADC 采样时,建议缩短 ADC 采样通道的外部走线距离;

- 2) ADC 的输入信号周边建议远离一些高频翻转信号;

- 3) 注意 ADC 采样通道的最高支持速率: N32H76X/N32H78X 系列在 ADC 输入时钟为 20MHZ 条件下, ADC 通道采样率不超过 5Msps;

- 4) 在 ADC 转换期间,芯片不支持修改 ADC 配置,如需修改配置,需要等待当前转换结束或者关闭 ADC 后,再进行配置:

- 5) 在使用某一 ADC 通道时,不能在其它未使用的 ADC 采样通道施加负压(比如-0.2V),如果施加了此负电压,会导致正常采样的 ADC 通道电压被拉低,导致读取的数据不准;

- 6) 在使用某一 ADC 通道时,不能在其它未使用的 ADC 采样通道施加高压 (大于 VDD 电压),如果施加了此高电压,会导致正常采样的 ADC 通道电压被拉高,导致读取的数据不准;

- 7) 在使用 ADC 时,ADC 的采样速率和 R<sub>AIN</sub> 是相关的,R<sub>AIN</sub> 越小采样速率越快,具体见下表:

图 1-7 ADC 输入口串联电阻的影响

#### ADC 采样时间表:

| 分辨率    | Rin (kΩ) | 最小采样时间(ns) |

|--------|----------|------------|

|        | 0        | 50         |

|        | 0.45     | 100        |

|        | 0.7      | 150        |

|        | 0.95     | 200        |

| 12-bit | 1.95     | 400        |

|        | 2.95     | 600        |

|        | 3.95     | 800        |

|        | 4.95     | 1000       |

|        | 9.95     | 2000       |

表 1-2 ADC 采样时间表

注:采样时间需根据输入时钟和ADC寄存器可选的采样周期综合配置,原则上ADC采样周期配置应大于等于表中最小采样周期数。

### 1.8 高速通信接口设计建议

#### 1.8.1 USBHS 接口

- 1、DPDM 走线需做阻抗控制,差分阻抗需为 90Ω±10%;

- 2、DPDM 走线需做等长匹配,差分对长度差控制在±5mil 内;

- 3、DPDM 走线需对称走线,避免直角拐弯,减少阻抗突变;

- 4、在 DPDM 线上靠近连接器处添加 ESD 二极管, 防止静电损坏;

- 5、确保 DPDM 差分线下有完整参考地平面,避免跨越分割,减少回流路径干扰;

- 6、DPDM 走线应尽量避开电源、时钟等高频噪声区域,在差分线周围增加屏蔽地过孔;

- 7、部分设计需在差分线末端串联 22Ω 电阻,抑制反射。

- 8、 当使用 USBHS 模块时, 需要使用外部 HSE 晶体作为时钟源, 且 HSE 频率只能是 10MHz、12MHz、19.2MHz、24MHz、25MHz、27MHz、30MHz 或 40MHz。

#### 1.8.2 MIPI 接口

- 1、MIPI 走线需做差分阻抗, 差分阻抗需控制为 100Ω±10%;

- 2、MIPI 走线需做等长匹配,差分对内等长误差需控制在 5mil 内,线对间误差不超过 10~20mil,可通过蛇形线调整长度:

- 3、MIPI 走线需对称走线,避免直角拐弯,减少阻抗突变;

- 4、确保 MIPI 走线有完整参考地平面,避免跨越分割,减少回流路径干扰;

- 5、MIPI 走线尽量减少过孔数量,建议不超过 2 个,换层时需对称打孔,并在过孔附近添加回流地孔以 优化信号回流路径,同时建议使用小孔过孔,以降低寄生电容影响:

- 6、MIPI 走线应尽量远离其他高速信号,与其保持至少3倍线宽线距,避免平行走线,同时在差分线周围要增加屏蔽地过孔;

- 7、为 MIPI 模块提供独立电源层,靠近电源引脚增加去耦电容,降低电源噪声。

### 1.8.3 EtherCAT/ETH接口

- 1、TXP/TXN,RXP/RXN 差分信号对,差分阻抗需控制为 100Ω±10%,同一对差分线的长度差需控制在 5mil 以内,以保持信号对称性,减少共模噪声和时序偏差;发送(TXP/TXN)与接收(RXP/RXN) 差分对的整体长度差建议控制在 50mil 以内,避免跨节点通信延迟不一致;

- 2、接口信号时钟线与数据线需做等长处理, EtherCAT 接口 TX\_CLK 与 TX[3:0]、RX\_CLK 与 RXD[3:0] 需组内等长, 长度差需控制在 50mil 以内; ETH GMII 接口 TX\_CLK 与 TX[7:0]、RX\_CLK 与 RXD[7:0] 需组内等长, 长度差需控制在 5mil 以内;

- 3、管理接口 MDC 与 MDIO 信号建议走线长度差<100mil,使用时需加电阻上拉,避免配置时序异常;

- 4、差分对走线应全程参考完整地平面,避免跨分割或换层;

- 5、避免直角走线,减少阻抗突变,可通过蛇形线调整走线长度;

- 6、 晶振尽量靠近 PHY 芯片, 时钟信号包地处理, 减少辐射干扰;

#### 1.8.4 SDRAM 接口

- 1、SDRAM 的片选引脚建议优先选用 SDRAM\_NCE0 与 SDRAM\_CKE0,这样 SDRAM 既可以跑代码, 又可以读写数据;选择 SDRAM NCE1 与 SDRAM CKE1 时,仅支持 SDRAM 的数据读写;

- 2、电源平面尽量完整,减少阻抗,靠近电源引脚增加去耦电容,降低电源噪声。;

- 3、时钟信号 CLK 优先布线,保持最短路径,远离其他高速信号;

- 4、数据线(DQ0~DQ15、LQDM、UDQM) 走线需组内等长,长度差需控制在 50mil 以内

- 5、地址线(A0~A12、BS0、BS1) 走线需组内等长,长度差需控制在100mil 以内;

- 6、控制信号线(CS/RAS/CAS/WE)走线需组内等长,长度差需控制在100mil以内;

- 7、地址/控制线相对 CLK 时钟线长度差需控制在 100mil 以内;

- 8、采用完整地平面,避免跨分割,确保低阻抗回流路径;

- 9、地址线、控制线、数据线、LCK 信号可端接一个 22~33Ω 电阻,减少信号反射,提升信号完整性。

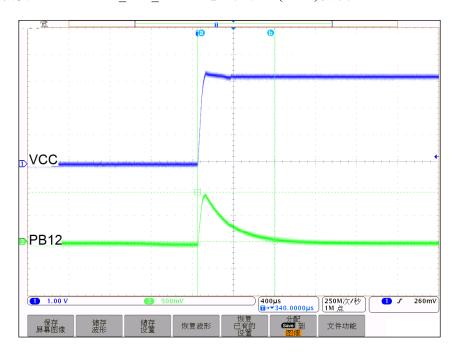

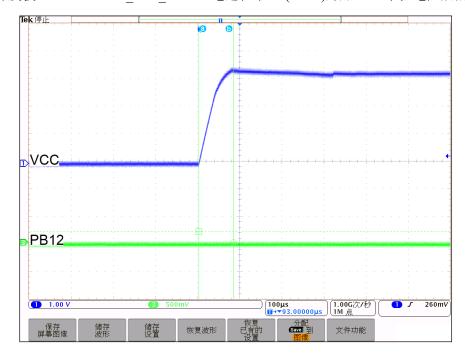

### 1.9 IO 上电脉冲处理

上电过程中由于 IO 处于高阻态及内部电路耦合特性,上电瞬间会引起 IO 上出现高电平脉冲(实际的高脉冲电压值请用户实测)。若该脉冲会影响其应用,建议在对应 IO 上挂适当电容( $1nF\sim100nF$ )或外加适当下拉电阻( $10K\sim100K$ )处理。

下图为开发板 N32H760VIB7 STB V1.0 上电过程中 IO(PB12)波形图:

图 1-8 上电过程 IO(PB12)波形

下图为开发板 N32H760VIB7 STB V1.0 上电过程中 IO(PB12)外加 10K 下拉电阻后的波形图:

图 1-9 上电过程 IO (PB12) 外加下拉电阻处理后波形

### 1.10 IO 耐压值

芯片使用时请注意各 IO 耐压值, 在数据手册引脚复用定义的 I/O 结构一栏, 标注了 FT: 5V tolerant IO, 这类型 IO 在与外部其它不同电压域的 IO 进行通讯时, 需要做电平转换。

|                | 封導        | 虔。        |            |            |            |                                | Fail   |                                                                                                                  |      | Fail | 可选的复用功能。 |  |

|----------------|-----------|-----------|------------|------------|------------|--------------------------------|--------|------------------------------------------------------------------------------------------------------------------|------|------|----------|--|

| TFBGA240+ 25 - | LQFP208 . | LQFP176 . | UFBGA169 . | 管脚。<br>名称。 | 类<br>型(i)。 | I/O<br>结<br>构 <sup>(2)</sup> 。 | 结 safe | 默认。                                                                                                              | 重定义。 |      |          |  |

| C3 ÷           | 1 ↔       | 1.0       | A2 &       | PE2 -      | IO &       | TT ÷                           | Yes ∘  | TRACECLK + SPI6_SCK + ETH1_MII_TXD3/ETH1_GMII_TXD3 + GTIMB1_ETR + DVP2_D0 + FEMC_A23 + USART5_RX + FDCAN4_TX +   | - 0  |      |          |  |

| ДЗ ф           | 2 &       | 2 &       | C3 &       | PE3 o      | IO &       | TT ÷                           | Yes ₽  | TRACED0 + ETH1_MII_TXD2/ETH1_GMII_TXD2 + SHRTIM2_EEV + GTIMB1_BRK + DVP2_D1 + FEMC_A19 + USART5_TX + FDCAN4_RX - | - 0  |      |          |  |

图 1-10 数据手册引脚复用定义的 I/O 结构

注: FT: 5V tolerant IO; TT: 3.3V standard IO。在使用芯片时需注意 IO 的耐压值。

### 1.11 防静电设计

### 1.11.1 PCB 设计

对于普通两层板的 PCB 设计,建议信号线周围做包地处理,PCB 板边也尽量做到铺地环绕。在成本允许的条件下,可以用四层板或多层板设计,在多层 PCB 中地线面作为一个重要的电荷源,可抵消静电放电源上的电荷,这有利于减小静电场带来的问题。PCB 地线面也可作为其对信号线的屏蔽体(当然,地线面的开口越大,其屏蔽效能就越低)。另外,如果发生放电,由于 PCB 板的地平面很大,电荷很容易注入到地线面中,而不是进入到信号线中。这样将有利于对元件进行保护,因为在引起元件损坏前,电荷可以泄放掉。

### 1.11.2 ESD 防护器件

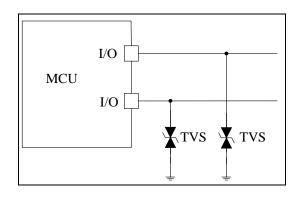

在实际产品设计中,芯片自身有一定的抗静电能力,N32H76X/N32H78X 系列 MCU ESD(HBM)模式下静电等级为+/-4KV,但如果有更高的 ESD 防护等级要求,且有芯片的管脚需要直接外接作为产品的输出或输入口,此时,芯片的管脚就直接暴露在产品的最外面,不能通过铺地等方式进行隔离。这种条件下,一般需要考虑外加 ESD 防护器件,TVS 管是一种典型的 ESD 保护器件,以下是典型的连接方式示例。

图 1-11 I/O 管脚上 TVS 连接方式

### 1.12 调试接口

N32H76X/N32H78X 系列芯片支持串行接口(SWD)和 JTAG 调试接口,详细应用请参考相关用户手册。

| 调试信号       | GPIO 引脚 |

|------------|---------|

| JTMS/SWDIO | PA13    |

| JTCK/SWCLK | PA14    |

| JTDI       | PA15    |

| JTDO       | PB3     |

| JNTRST     | PB4     |

表 1-3 调试接口

# 1.13 BOOT 串口接口

N32H76X/N32H78X 系列芯片支持 BOOT 串口通讯,串口接口如下表:

| BOOT 串口   | GPIO 引脚 |

|-----------|---------|

| USART1_TX | PA9     |

| USART1_RX | PA10    |

表 1-4 串口接口

### 1.14 各模块设计注意事项

#### 1.14.1 SDRAM

1) SDRAM 的片选引脚建议优先选用 SDRAM\_NCE0 与 SDRAM\_CKE0,这样 SDRAM 既可以跑代码, 又可以读写数据;选择 SDRAM NCE1 与 SDRAM CKE1 时,仅支持 SDRAM 的数据读写;

#### 1.14.2 SDMMC

1) 使用 SD 卡时,需要注意设计一个 NRST 引脚用于通过 IO 上下拉的形式对 SD 卡进行上下电,避免 MCU 复位而卡没有掉电导致的 MCU 端和卡端 IO 电压不匹配;

2) CLKIN 引脚是必须的,设计上需要预留这个引脚

#### 1.14.3 **USBHS**

1) 当使用 USBHS 模块时, 需要使用外部 HSE 晶体作为时钟源, 且 HSE 频率只能是 10MHz、12MHz、19.2MHz、24MHz、25MHz、27MHz、30MHz 或 40MHz。

#### **1.14.4 VREFBUF**

1) 当使能内部参考源 VREFBUF 时, VREF+管脚不能外接电压。

### 2. 整体设计建议

#### 1) 印制电路板

建议使用有专门独立的接地层(VSS)和专门独立的供电层(VDD)的多层印制电路板,从而能提供好的耦合性能和屏蔽效果。在实际应用中,如考虑成本因素不能使用多层印制电路板,那么在设计电路时就需保证一个好的接地和供电的结构。

#### 2) 器件位置

在 PCB 设计时根据各器件对 EMI 影响的不同,需把不同的电路分开布局。比如,大电流电路、低电压电路、以及高频器件等。从而减少 PCB 上的交叉耦合。

#### 3) 接地和供电(VSS, VDD)

各模块(模拟电路、数字电路、敏感度低的电路)都应该单独接地,数字地和模拟地分开,所有的地最终都应在一个点上连到一起。根据印制线路板电流的大小,尽量加粗电源线宽度,减少环路电阻。同时,电源线、地线的走向和电流的方向应尽量一致,且电源应尽量靠近地线,减小回路的区域。这样有助于增强抗噪声能力。PCB上没有器件的区域,需要填充为地,以提供好的屏蔽效果。

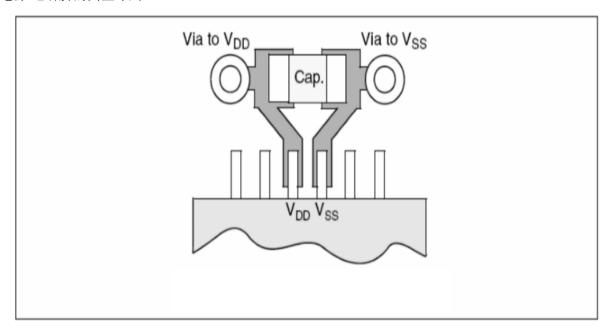

#### 4) 去耦合

所有的电源引脚都需要适当的连接到电源。这些连接,包括焊盘、连线和过孔应该具备尽量小的阻抗。通常采用增加连线宽度的办法,同时每对 VDD 与 VSS 引脚都必须在靠近芯片处放置去耦电容。下图为电源/地引脚的典型布局。

图 2-1 VDD/VSS 引脚的典型布局

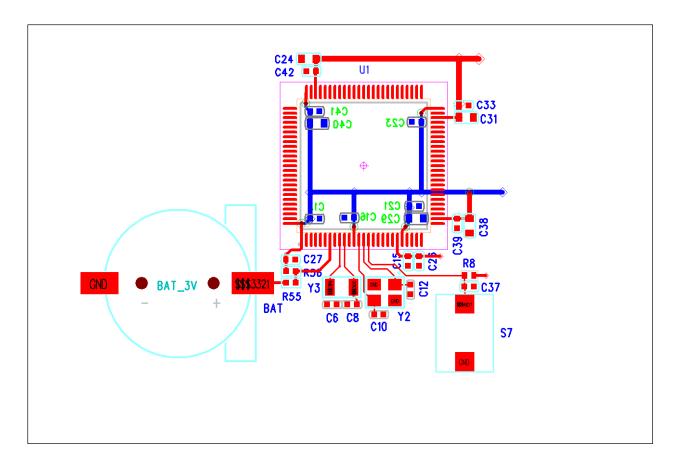

# 3. PCB LAYOUT 参考

图 3-1 LQFP100 封装 PCB LAYOUT 参考图

#### 注:

- 1、PCB LAYOUT 设计时,每一个电源管脚都需要就近放置去耦电容;

- 2、HSE 和 LSE 的外部晶体及走线尽可能在周围做包地处理,晶体下面一层靠近晶体的区域也需要铺地,不能有信号线穿过,防止信号线干扰晶体信号;

- 3、HSE 和 LSE 用作晶振时,走线不宜过长,避免天线效应。

# 4. 历史版本

| 版本     | 日期             | 备注                                                                                                                       |  |  |

|--------|----------------|--------------------------------------------------------------------------------------------------------------------------|--|--|

| V1.0.0 | 2025-4-20 创建文档 |                                                                                                                          |  |  |

| V1.1.0 | 2025-5-16      | 1.更新备用电池章节 VBAT 引脚连接注意事项 2.修改章节 EtherCAT/ETH 接口设计建议描述 3.删除表 1-2 ADC 采样时间表关于 10-bit 描述 4.补充 LDO 选型要求以及 DCDC 供电 VCAP 的推荐电路 |  |  |

|        |                |                                                                                                                          |  |  |

### 5. 声明

国民技术股份有限公司(下称"国民技术")对此文档拥有专属产权。依据中华人民共和国的法律、条约以及世界其他法域相适用的管辖,此文档及其中描述的国民技术产品(下称"产品")为公司所有。

国民技术在此并未授予专利权、著作权、商标权或其他任何知识产权许可。所提到或引用的第三方名称或品牌(如有)仅用作区别之目的。

国民技术保留随时变更、订正、增强、修改和改良此文档的权利,恕不另行通知。请使用人在下单购买前联系国民技术获取此文档的最新版本。

国民技术竭力提供准确可信的资讯,但即便如此,并不推定国民技术对此文档准确性和可靠性承担责任。使用此文档信息以及生成产品时,使用者应当进行合理的设计、编程并测试其功能性和安全性,国民技术不对任何因使用此文档或本产品而产生的任何直接、间接、意外、特殊、惩罚性或衍生性损害结果承担责任。

国民技术对于产品在系统或设备中的应用效果没有任何故意或保证,如有任何应用在其发生操作不当或故障情况下,有可能致使人员伤亡、人身伤害或严重财产损失,则此类应用被视为"不安全使用"。

不安全使用包括但不限于:外科手术设备、原子能控制仪器、飞机或宇宙飞船仪器、所有类型的安全装置以及其他旨在支持或维持生命的应用。

所有不安全使用的风险应由使用人承担,同时使用人应使国民技术免于因为这类不安全使用而导致被 诉、支付费用、发生损害或承担责任时的赔偿。

对于此文档和产品的任何明示、默示之保证,包括但不限于适销性、特定用途适用性和不侵权的保证责任,国民技术可在法律允许范围内进行免责。

未经明确许可,任何人不得以任何理由对此文档的全部或部分进行使用、复制、修改、抄录和传播。