## **User Guide**

# N32G45x\_N32G4FR\_N32WB452 Series PLL user guide

### Introduction

The N32G45x\_N32G4FR\_N32WB452 series of microcontrollers from NSING are equipped with a built-in PLL (Phase-Locked Loop) module, which provides a clock for the system.

This document aims to help users correctly use the PLL of the N32G45x\_N32G4FR\_N32WB452 series and improve the operational stability of the PLL.

#### Contents

| 1. Overview of PLL in N32G45x_N32G4FR_N32WB452 series           | 3 |

|-----------------------------------------------------------------|---|

| 1.1 PLL features                                                |   |

| 1.2 Basic Working Principle of PLL                              |   |

| 2. N32G45x_N32G4FR_N32WB452 working mode                        |   |

| 3. Precautions for Using PLL in N32G45x_N32G4FR_N32WB452 Series |   |

| 3.1 PLL Configuration Process                                   | 6 |

| 3.2 PLL Clock Sources                                           | 6 |

| 3.3 PLL Output Frequency                                        | 6 |

| 3.4 USB clock frequency                                         | 7 |

| 4. Version History                                              | 8 |

| 5 Notice                                                        | c |

## 1. Overview of PLL in N32G45x N32G4FR N32WB452 series

#### 1.1 PLL features

- Input frequency range of Fin: 4 MHz to 32 MHz

- Input frequency range of PFD: 4 MHz to 32 MHz

- Output frequency range:

- 32 MHz to 144 MHz

- Reference clock options:

- HSI clock

- HSE clock

- Power supply voltage: 1.8V-3.6V

- The PLL multiplication factor must be 8 or greater to ensure loop stability

#### 1.2 Basic Working Principle of PLL

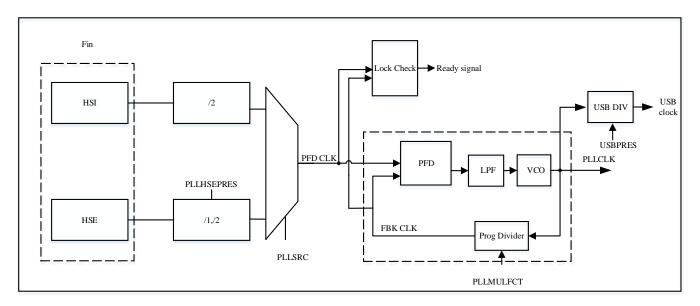

The PLL of the N32G45x\_N32G4FR\_N32WB452 series integrate a Phase Frequency Detector (PFD), Charge Pump (CP), Low-Pass Filter (LPF), Voltage-Controlled Oscillator (VCO) and other related modules. All basic building blocks as well as fully programmable frequency dividers are integrated within the core. The maximum output frequency of the PLL can reach 144MHz. They support an operating voltage range of 1.8V to 3.6V and an ambient temperature range of -40°C to 105°C.

# 2. N32G45x\_N32G4FR\_N32WB452 working mode

### PLL working mode

| MCU power mode | PLL clock source | RCC_CFG. PLLHSERES | RCC_CTRL.PLLEN | RCC_CFG.PLLSRC |

|----------------|------------------|--------------------|----------------|----------------|

| Run mode       | HSI/2            | -                  | 1              | 0              |

|                | HSE              | PLLHSERES=0        | 1              | 1              |

|                | HSE/2            | PLLHSERES=1        | 1              | 1              |

| Sleep mode     | HSI/2            | -                  | 1              | 0              |

|                | HSE              | PLLHSERES=0        | 1              | 1              |

|                | HSE/2            | PLLHSERES=1        | 1              | 1              |

| STOP0 mode     | -                | -                  | 0              | -              |

| STOP2 mode     | -                | -                  | 0              | -              |

| STANDBY mode   | -                | -                  | 0              | -              |

## 3. Precautions for Using PLL in N32G45x\_N32G4FR\_N32WB452 Series

#### 3.1 PLL Configuration Process

- 1. Configure the PLL clock source, selecting HSI/2, HSE, or HSE/2 as the PLL clock source.

- 2. Configure the PLL multiplication factor.

- 3. Enable the PLL.

- 4. Wait for the PLL ready flag.

- 5. Switch the system clock to PLL.

Note: The PLL configuration cannot be dynamically modified. If it is necessary to modify the PLL configuration while the PLL is operating as the system clock source, the system clock source must first be switched to HSE or HSI. After the switch is completed, disable the PLL, and then execute the above configuration process (steps 1, 2, 3, 4, 5).

#### 3.2 PLL Clock Sources

Reference clock for PLL PFD:

When PLLSRC=0, we select the HSI clock as the reference clock for the PLL, and its frequency is calculated as follows:

$$f_{pfd} = \frac{f_{HSI}}{2}$$

When PLLSRC=1, we select the HSE clock as the reference clock for the PLL, and its frequency is calculated as follows:

$$f_{pfd} = \frac{f_{HSE}}{\text{PLLHSEPRE} + 1}$$

Note: The PFD clock frequency range is 4 MHz ~ 32 MHz.

# 3.3 PLL Output Frequency

The PLL multiplication factor can be configured by setting RCC\_CFG.PLLMULFCT[4:0]. The multiplication factor "M" is as follows:

00000: PLL input clock  $\times 2$

00001: PLL input clock ×3

00010: PLL input clock ×4

. . . . . .

11101: PLL input clock  $\times$  30

11110: PLL input clock ×31

11111: PLL input clock ×32

Note: The PLL multiplication factor must be 8 or greater to ensure loop stability.

$$f_{PLL} = M * f_{pfd}$$

The PLL output frequency range is 32 MHz to 144 MHz.

### 3.4 USB clock frequency

The USB clock frequency is 48MHz. The USB frequency is derived through PLL frequency division, and the division must be 1, 1.5, 2, or 3. Therefore, when using USB, the PLL frequency must be 48MHz, 72MHz, 96MHz, or 144MHz. Due to the high precision requirements of the USB clock, an external HSE must be used as the PLL clock source.

# 4. Version History

| Version | Date       | Changes         |  |

|---------|------------|-----------------|--|

| V1.0.0  | 2025.08.08 | Initial release |  |

#### 5. Notice

This document is the exclusive property of NSING TECHNOLOGIES PTE. LTD. (Hereinafter referred to as NSING). This document, and the product of NSING described herein (Hereinafter referred to as the Product) are owned by NSING under the laws and treaties of Republic of Singapore and other applicable jurisdictions worldwide. The intellectual properties of the product belong to NSING Technologies Inc. and NSING Technologies Inc. does not grant any third party any license under its patents, copyrights, trademarks, or other intellectual property rights. Names and brands of third party may be mentioned or referred thereto (if any) for identification purposes only. NSING reserves the right to make changes, corrections. enhancements, modifications, and improvements to this document at any time without notice. Please contact NSING and obtain the latest version of this document before placing orders. Although NSING has attempted to provide accurate and reliable information, NSING assumes no responsibility for the accuracy and reliability of this document. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. In no event shall NSING be liable for any direct, indirect, incidental, special, exemplary, or consequential damages arising in any way out of the use of this document or the Product. NSING Products are neither intended nor warranted for usage in systems or equipment, any malfunction or failure of which may cause loss of human life, bodily injury or severe property damage. Such applications are deemed, Insecure Usage'. Insecure usage includes, but is not limited to: equipment for surgical implementation, atomic energy control instruments, airplane or spaceship instruments, all types of safety devices, and other applications intended to supporter sustain life. All Insecure Usage shall be made at user's risk. User shall indemnify NSING and hold NSING harmless from and against all claims, costs, damages, and other liabilities, arising from or related to any customer's Insecure Usage Any express or implied warranty with regard to this document or the Product, including, but not limited to. The warranties of merchantability, fitness for a particular purpose and non-infringement are disclaimed to the fullest extent permitted by law. Unless otherwise explicitly permitted by NSING, anyone may not use, duplicate, modify, transcribe or otherwise distribute this document for any purposes, in whole or in part.