## 使用指南

## N3247x\_48x系列PLL使用指南

## 简介

国民技术微控制器 N3247x\_48x 系列内置 1 个 PLL 模块,为系统提供时钟。 本文档旨在帮助用户正确使用 PLL,提高 PLL 工作稳定性。

#### 目录

| 1.  | PLL 简介    | 1 |

|-----|-----------|---|

|     | LL 模块框图   |   |

|     | LL 参数特性   |   |

| 2.  | PLL 工作模式  | 1 |

| 3.  | PLL 配置及限制 | 2 |

|     | 寄存器接口     |   |

|     | 项率计算      |   |

| 3.2 | 配置流程      | 3 |

| 4.  | 历史版本      | 4 |

| 5.  | 声明        | 5 |

网址: https://www.nsingtech.com 邮编: 518057

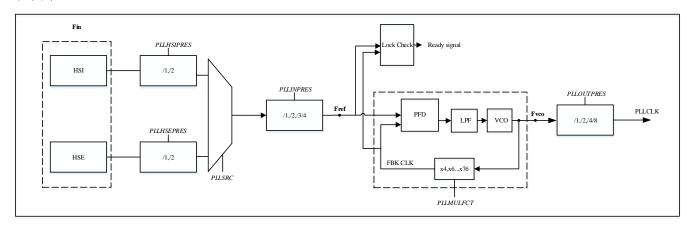

#### 1. PLL 简介

#### 1.1 PLL 模块框图

PLL (Phase-Loop-Lock)模块内部集成了相位频率检测器 (PFD)、电荷泵 (CP)、低通环路滤波器 (LPF)、压控振荡器 (VCO)及其他相关模块。所有基本构建模块以及全可编程分频器均集成在核心内部。PLL输出频率最高可达240MHz。

#### 1.2 PLL 参数特性

- 输入频率 Fin 范围: 4 MHz 至 50MHz

- Fref 频率范围: 4 MHz 至 25MHz

- Fvco 频率范围: 64MHz 至 500MHz

- PLL 输出频率范围: 最大 240MHz

- 倍频系数范围: 8 倍至 76 倍

- 参考时钟源选项:

- HSI 时钟

- HSE 时钟

- 电源电压: 1.8V-3.6V

- 结温范围: -40°C~125°C

#### 2. PLL 工作模式

PLL 可工作在 Run、sleep 模式下, STOPO、standby、VBAT 模式下自动关闭。

| MCU 功耗模式 | PLL 时钟源 | 寄存器配置         | RCC_CFG.PLLSRC | RCC_CTRL.PLLEN |

|----------|---------|---------------|----------------|----------------|

|          | HSI     | PLLHSIPRES=0  | 0              | 1              |

| Run 模式   | HSI/2   | PLLHSIPRES=1  | 0              | 1              |

| Kun 侯八   | HSE     | PLLHSEPRES=0  | 1              | 1              |

|          | HSE/2   | PLLHSEPRES =1 | 1              | 1              |

1

|            | HSI   | PLLHSIPRES=0 | 0 | 1 |

|------------|-------|--------------|---|---|

| Sleep 模式   | HSI/2 | PLLHSIPRES=1 | 0 | 1 |

| Sieep 模式   | HSE   | PLLHSEPRES=0 | 1 | 1 |

|            | HSE/2 | PLLHSEPRES=1 | 1 | 1 |

| STOP0 模式   | -     | -            | - | 0 |

| STANDBY 模式 | -     | -            | - | 0 |

| VBAT 模式    | -     | -            | - | 0 |

## 3. PLL 配置及限制

## 3.1 寄存器接口

| 寄存器         | Bit             | 描述(具体见用户手册)                                                                                                                                      |  |  |

|-------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| DCC CTDI    | PLLRDF          | PLL 时钟就绪标志位                                                                                                                                      |  |  |

| RCC_CTRL    | PLLEN           | PLL 使能位                                                                                                                                          |  |  |

|             | PLLMULFCT[5:0]  | PLL 倍频系数<br>倍频系数由软件写入,Fvco=Fref*M(M = 2*PLLMULFCT+4)。这些位只<br>能在 PLL 被禁用时写入。<br>注意: 需配置 Fvco 频率在 64MHz 至 500MHz 范围内<br>注意: 需配置倍频系数在 8 倍至 76 倍频范围内 |  |  |

| RCC_CFG     | PLLHSIPRES      | PLL 输入的 HSI 预分频器<br>由软件置位和清零,配置进入 PLL 之前 HSI 的分频。该位只能在 PLL<br>禁用时写入。                                                                             |  |  |

|             | PLLHSEPRES      | PLL 输入的 HSE 预分频器<br>由软件置位和清零,配置进入 PLL 之前 HSE 的分频。该位只能在 PLL<br>禁用时写入。                                                                             |  |  |

|             | PLLSRC          | PLL 时钟源<br>由软件置位和清零,配置选择 PLL 时钟源。该位只能在 PLL 禁用时写<br>入。                                                                                            |  |  |

|             | PLLOUTPRES[1:0] | PLL 输出分频<br>注意: 需配置 PLL 不超过 240MHz<br>注意: 配置为不分频时,占空比偏差为 50%+-5%,功耗较小; 配置为分<br>频时,占空比偏差 50%+-1%,但功耗更大                                            |  |  |

|             | PLLINPRES[1:0]  | PLL 输入分频<br>注意: 需配置 Fref 频率在 4 MHz 至 25MHz 范围内                                                                                                   |  |  |

|             | DEADZEN         | PLL 监频监相器死区调整                                                                                                                                    |  |  |

| RCC_PLLCTRL | LPFC2[2:0]      | PLL 滤波环路的积分电容控制<br>根据 RCC_CFG.PLLMULFCT[5:0]对应的倍频系数选择不同的配置。<br>4~24 倍放大频率:配置 6<br>24~40 倍放大频率:配置 6<br>40~76 倍放大频率:配置 6                           |  |  |

|             | LPFR[3:0]       | PLL 滤波环路的零点电阻控制<br>根据 RCC_CFG.PLLMULFCT[5:0]对应的倍频系数选择不同的配置。<br>4~24 倍放大频率: 配置 3<br>24~40 倍放大频率: 配置 7<br>40~76 倍放大频率: 配置 12                       |  |  |

|             | LPFC1[3:0]      | PLL 滤波环路的旁路电容控制<br>根据 RCC_CFG.PLLMULFCT[5:0]对应的倍频系数选择不同的配置。<br>4~24 倍放大频率:配置 4<br>24~40 倍放大频率:配置 4                                               |  |  |

40~76 倍放大频率: 配置 4

#### 3.2 频率计算

Fref 频率 (4~25M) 计算如下:

当 PLLSRC=0 时,选择 HSI 时钟作为参考时钟源

$$f_{ref} = \frac{f_{HSI}}{\text{PLLHSIPRES} * \text{PLLINPRES}}$$

当 PLLSRC=1 时,选择 HSE 时钟作为参考时钟源

$$f_{ref} = \frac{f_{HSE}}{\text{PLLHSEPRES} * PLLINPRES}$$

Fvco 频率 (64~500M) 计算如下:

$$f_{vco} = f_{ref} * PLLMULFCT$$

注意: PLLMULFCT 配置的倍频系数应在8倍~76倍之间

PLL 输出频率 (8~240M) 计算如下:

$$f_{pll} = \frac{f_{vco}}{\text{PLLOUTPRES}}$$

#### 3.2 配置流程

- 1. 配置 PLL 时钟源,选择 HSI, HSI/2, HSE 或 HSE/2 作为 PLL 时钟源

- 2. 配置 PLL 输入分频系数, 倍频系数, 输出分频系数, LPFC1\ LPFC2\ LPFR 滤波环路参数

- 3. 使能 PLL

- 4. 等待 PLL ready 标志

- 5. 切换系统时钟到 PLL

注意: VDD 电压在 1.7V 以上, 系统时钟才允许切换到 PLL, 可通过 PVD 监控 VDD 实现。

注意: PLL 配置不能动态修改,如果在PLL 作为系统时钟源运行时需要修改 PLL 配置,必须先将系统时钟源切换成 HSE 或者 HSI,切换完成后关闭 PLL 使能,再执行上述配置流程。

3

# 4. 历史版本

| 版本     | 日期        | 备注   |

|--------|-----------|------|

| V1.0.0 | 2025.8.18 | 初始版本 |

网址: https://www.nsingtech.com 邮编: 518057

#### 5. 声明

国民技术股份有限公司(下称"国民技术")对此文档拥有专属产权。依据中华人民共和国的法律、条约以及世界其他法域相适用的管辖,此文档及其中描述的国民技术产品(下称"产品")为公司所有。

国民技术在此并未授予专利权、著作权、商标权或其他任何知识产权许可。所提到或引用的第三方名称或品牌 (如有)仅用作区别之目的。

国民技术保留随时变更、订正、增强、修改和改良此文档的权利,恕不另行通知。请使用人在下单购买前联系国民技术获取此文档的最新版本。

国民技术竭力提供准确可信的资讯,但即便如此,并不推定国民技术对此文档准确性和可靠性承担责任。

使用此文档信息以及生成产品时,使用者应当进行合理的设计、编程并测试其功能性和安全性,国民技术不对 任何因使用此文档或本产品而产生的任何直接、间接、意外、特殊、惩罚性或衍生性损害结果承担责任。

国民技术对于产品在系统或设备中的应用效果没有任何故意或保证,如有任何应用在其发生操作不当或故障情况下,有可能致使人员伤亡、人身伤害或严重财产损失,则此类应用被视为"不安全使用"。

不安全使用包括但不限于: 外科手术设备、原子能控制仪器、飞机或宇宙飞船仪器、所有类型的安全装置以及 其他旨在支持或维持生命的应用。

所有不安全使用的风险应由使用人承担,同时使用人应使国民技术免于因为这类不安全使用而导致被诉、支付 费用、发生损害或承担责任时的赔偿。

对于此文档和产品的任何明示、默示之保证,包括但不限于适销性、特定用途适用性和不侵权的保证责任,国民技术可在法律允许范围内进行免责。

未经明确许可,任何人不得以任何理由对此文档的全部或部分进行使用、复制、修改、抄录和传播。

网址: https://www.nsingtech.com 邮编: 518057