# ES\_N32WB03x Series Errata Sheet V1.0

#### Contents

| 1 ERRATA SHEET                                                                        | 1 |

|---------------------------------------------------------------------------------------|---|

| 2 SYSTEM CLOCK CONTROL (RCC)                                                          | 2 |

| 2.1 NOTE TO USE OF RCC_LSCTRL REGISTER                                                | 2 |

| 2.2 RCC_AHBRST's ADCRST BIT RESET ADC                                                 | 2 |

| 3 LOWER POWER UNIVERSAL ASYNCHRONOUS RECEIVER-TRANSMITTER (LPUART)                    | 2 |

| 3.1 WHEN LSI 32K AS CLOCK SOURCE AND 9600 BAUD RATE, BYTE WAKE-UP IS ABNORMAL         | 2 |

| 4 SERIAL PERIPHERAL INTERFACE (SPI)                                                   | 2 |

| 4.1 SPI                                                                               |   |

| 4.1.1 SPI baud rate setup                                                             | 2 |

| 4.1.2 CRC calibration in slave mode                                                   | 3 |

| 4.1.3 When the Bluetooth protocol stack is used, SPI1 interrupts and fails to respond | 3 |

| 5 I2C INTERFACE                                                                       | 3 |

| 5.1 ABNORMAL SIGNAL INTERFERENCE                                                      | 3 |

| 6 KEY SCAN (KEYSCAN)                                                                  | 3 |

| 6.1 RETENTION VOLTAGE REQUIREMENT FOR KEYSCAN IN SLEEP MODE                           | 3 |

| 7 ADC CLOCK                                                                           |   |

| 7.1 CONFIGURATION OF ADC CLOCK                                                        | 4 |

| 8 CHIP SILK SCREEN PRINTING AND VERSION DESCRIPTION                                   | 4 |

| 9 VERSION HISTORY                                                                     | 5 |

| 10 NOTICE                                                                             | 6 |

## 1 Errata Sheet

**Table 1-1 Errata Overview**

|                                                                     |                           | Chip version                                                                                                                                           |           |           |

|---------------------------------------------------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|

| Errata links                                                        |                           |                                                                                                                                                        | Version D | Version E |

| 2: Reset and Clock                                                  | 2.1: Note to              | use of RCC_LSCTRL register                                                                                                                             | •         | •         |

| Control (RCC)                                                       | 2.2: RCC_A                | HBRST's ADCRST bit reset ADCl                                                                                                                          | •         | •         |

| 3: Lower Power Universal Asynchronous Receiver-Transmitter (LPUART) | 3.1: When LS byte wake-up | SI 32K as clock source and 9600 baud rate, is abnormal                                                                                                 |           |           |

| 4: Serial Peripheral<br>Interface (SPI)                             | 4.1: SPI                  | 4.1.1: SPI baud rate setup 4.1.2: CRC calibration in slave mode 4.1.2: When the Bluetooth protocol stack is used, SPI1 interrupts and fails to respond |           | •         |

| 5: I2C Bus Interface                                                | 5.1: Abnorma              | al signal interference                                                                                                                                 | •         | •         |

| 6: Key Scan<br>(KEYSCAN)                                            |                           | tering the Sleep mode, part of chips cannot ugh KEYSCAN.                                                                                               | •         | •         |

| 7: ADC Clock                                                        | 7.1: Configur             | ration of ADC clock                                                                                                                                    | •         | •         |

| ESD                                                                 | ESD Enhance               | ement(±3KV(HBM))                                                                                                                                       | /         | •         |

Note: " /" means this version is not applicable; " ●" means this version is applicable to this erratum description.

## 2 System Clock Control (RCC)

#### 2.1 Note to use of RCC\_LSCTRL register

#### **Description**

After waking up from the Sleep mode, if we operate the register RCC\_CFG, the register RCC\_LSCTRL will reset to the default value.

#### **Solution**

After waking up from the Sleep mode, first write in the register RCC\_LSCTRL, and then operate the register RCC\_CFG.

### 2.2 RCC\_AHBRST's ADCRST bit reset ADC

#### **Description**

Setting the RCC\_AHBPRST register's ADCRST bit cannot correctly reset the ADC module.

#### Solution

When we need to reset the ADC module, manually assign default value to all ADC module registers.

## 3 Lower Power Universal Asynchronous Receiver-Transmitter (LPUART)

## 3.1 When LSI 32K as clock source and 9600 baud rate, byte wake-up is

#### abnormal

#### **Description**

When 32K is used as clock source for LPUART, due to indivisibility between baud rate and clock source, the baud rate will be devious, resulting in wrong byte judgement when waking up, so it cannot wake up.

#### **Solution 1**

When LSI needs to be used as LPUART clock source, it is recommended to use LSI 32.768K.

#### **Solution 2**

Use LSE as the clock source of LPUART.

## 4 Serial Peripheral Interface (SPI)

#### 4.1 **SPI**

#### 4.1.1 SPI baud rate setup

#### **Description**

When in the SPI master mode and CRC calibration function are enabled, and the SPI clock frequency is above 8MHz, the CRC calibration is abnormal.

#### **Solution**

When in the SPI master mode and CRC calibration function are enabled, the SPI clock frequency is no more than 8MHz.

#### 4.1.2 CRC calibration in slave mode

#### **Description**

When SPI works in the slave mode and has enabled CRC calibration, even the NSS pin is of high level, as long as SPI receives the clock signal, it will still conduct CRC calculation.

#### **Solution**

Before CRC calibration, clear the CRC data register first, so that the master and slave devices are synchronized in CRC calibration.

#### 4.1.3 When the Bluetooth protocol stack is used, SPI1 interrupts and fails to respond

#### **Description**

When the Bluetooth protocol stack is enabled, the ROM interrupt vector table is used, but this interrupt vector table does not map out SPI1 interrupt callback function, so it cannot be called back.

#### **Solution**

Use DMA receiver or SPI2 module.

#### 5 I2C Interface

#### 5.1 Abnormal signal interference

#### **Description**

During the I2C operation process, SCL and SDA might be disturbed by glitch during communication, resulting in abnormal communication.

#### **Solution**

- 1. Reduce interference; (for example: adding filtering circuits such as capacitors on the I2C bus)

- 2. Implement a peripheral recovery mechanism; (configure SCL as an IO mode and continuously generate 9 clock pulses onto the clock bus, forcing the slave device to release its ACK bit, thereby releasing SDA to high level and restoring the bus to an idle state)

- 3. Use IO software to simulate I2C.

## 6 Key Scan (KEYSCAN)

# 6.1 Retention voltage requirement for KEYSCAN in Sleep mode Description

Under the sleep mode, KEYSCAN requires higher retention voltage, or there might be the risks that KEYSCAN and EXTI3 functions cannot wake up the chip.

#### **Solution**

Increase the retention voltage . Configuration:  $*(uint32\ t^*)0x40007014 = 0x00000818$ .

#### 7 ADC clock

## 7.1 Configuration of ADC clock

#### **Description**

The ADC clock is HSE, if the hardware board without 32M HSE crystal and without BLE function, the ADC will be sampling anomaly.

#### **Solution**

Configure the HSI as ADC clock, configuration: \*(uint32 t\*)0x40011004 = 0x40.

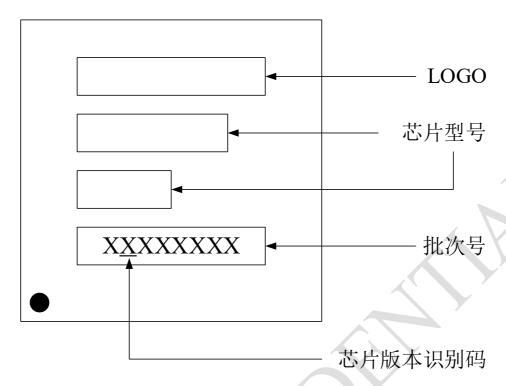

## 8 Chip Silk Screen Printing and Version Description

芯片型号 Chip model 批次号 Batch number 芯片版本识别码 Chip version identification code

## 9 Version History

| Date       | Version | Modification    |

|------------|---------|-----------------|

| 2025/08/29 | V1.0    | Initial version |

#### 10 Notice

This document is the exclusive property of NSING TECHNOLOGIES PTE. LTD. (Hereinafter referred to as NSING). This document, and the product of NSING described herein (Hereinafter referred to as the Product) are owned by NSING under the laws and treaties of Republic of Singapore and other applicable jurisdictions worldwide. The intellectual properties of the product belong to NSING Technologies Inc. and NSING Technologies Inc. does not grant any third party any license under its patents, copyrights, trademarks, or other intellectual property rights. Names and brands of third party may be mentioned or referred thereto (if any) for identification purposes only. NSING reserves the right to make changes, corrections. enhancements, modifications, and improvements to this document at any time without notice. Please contact NSING and obtain the latest version of this document before placing orders. Although NSING has attempted to provide accurate and reliable information, NSING assumes no responsibility for the accuracy and reliability of this document. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. In no event shall NSING be liable for any direct, indirect, incidental, special, exemplary, or consequential damages arising in any way out of the use of this document or the Product. NSING Products are neither intended nor warranted for usage in systems or equipment, any malfunction or failure of which may cause loss of human life, bodily injury or severe property damage. Such applications are deemed, Insecure Usage'. Insecure usage includes, but is not limited to: equipment for surgical implementation, atomic energy control instruments, airplane or spaceship instruments, all types of safety devices, and other applications intended to supporter sustain life. All Insecure Usage shall be made at user's risk. User shall indemnify NSING and hold NSING harmless from and against all claims, costs, damages, and other liabilities, arising from or related to any customer's Insecure Usage Any express or implied warranty with regard to this document or the Product, including, but not limited to. The warranties of merchantability, fitness for a particular purpose and non-infringement are disclaimed to the fullest extent permitted by law. Unless otherwise explicitly permitted by NSING, anyone may not use, duplicate, modify, transcribe or otherwise distribute this document for any purposes, in whole or in part.