N32G435 系列勘误手册 V2.1.0

# 目录

| 1 | 勘误       | 误列表1                                                           |    |  |  |  |  |

|---|----------|----------------------------------------------------------------|----|--|--|--|--|

| 2 | 电源       | 控制(PWR)                                                        | 3  |  |  |  |  |

|   | 2.1      | 系统时钟切换                                                         | 3  |  |  |  |  |

|   | 2.2      | LP RUN 模式切换到 Stop2 模式                                          | 3  |  |  |  |  |

|   | 2.3      | 电源掉电后再上电                                                       | 3  |  |  |  |  |

| 3 | 复位       | 和时钟控制(RCC)                                                     | 4  |  |  |  |  |

|   | 3.1      | 从 Run 模式进入 Stop2 模式                                            | 4  |  |  |  |  |

|   | 3.2      | LSE-CSS 故障检测                                                   | 4  |  |  |  |  |

| 4 | GPI      | )和 AFIO                                                        | 5  |  |  |  |  |

|   | 4.1      | GPIO 模拟功能                                                      | 5  |  |  |  |  |

| 5 | 模拟       | /数字转换(ADC)                                                     | 5  |  |  |  |  |

|   | 5.1      | ADC 数据左对齐                                                      | 5  |  |  |  |  |

|   | 5.2      | ADC 注入通道触发规则通道转换                                               | 5  |  |  |  |  |

|   | 5.3      | ADC 模拟看门狗                                                      | 6  |  |  |  |  |

|   | 5.4      | DMA 搬移 ADC 数据                                                  | 6  |  |  |  |  |

|   | 5.5<br>题 | 当 ENDC(或 JENDC)标志置位后立即去读取 ADC 数据寄存器 ADC_DAT (或 ADC_JDATx)值异常的6 | ij |  |  |  |  |

| 6 | 串行       | 外设接口(SPI)                                                      | 7  |  |  |  |  |

|   | 6.1      | SPI 接口                                                         | 7  |  |  |  |  |

|   | 6.1.1    | SPI 波特率设置                                                      | 7  |  |  |  |  |

|   | 6.1.2    | 从模式 CRC 校验                                                     | 7  |  |  |  |  |

|   | 6.1.3    | SPI CLK GPIO 配置                                                | 7  |  |  |  |  |

|   | 6.2      | I2S 接口                                                         | 8  |  |  |  |  |

|   | 6.2.1    | PCM 长帧模式                                                       | 8  |  |  |  |  |

| 7 | I2C      | 接口                                                             | 9  |  |  |  |  |

|   | 7.1      | 当前字节传输前必须被管理的软件事件                                              | 9  |  |  |  |  |

|   | 7.2      | 单次读取单或双字节时的注意事项                                                | 9  |  |  |  |  |

|   | 7.3      | 与其他外设同时使用 DMA                                                  | 10 |  |  |  |  |

|   | 7.4      | 异常信号干扰                                                         | 10 |  |  |  |  |

地址:深圳市南山区高新北区宝深路109号国民技术大厦 电话: +86-755-86309900 传真: +86-755-86169100 网址: https://www.nsingtech.com 邮编: 518057

| 8  | 通    | <b>鱼用同步异步接收器(USART)</b> | 12 |

|----|------|-------------------------|----|

|    | 8.1  | 校验错误标志                  | 12 |

|    | 8.2  | RTS 硬件流控                | 12 |

| 9  | 调    | 周试接口(DBG)               | 13 |

|    | 9.1  | Debug 寄存器               | 13 |

| 10 | 定    | E时器(TIM)                | 14 |

|    | 10.1 | 定时器重复捕获检测               | 14 |

| 11 | 比    | L 较器 COMP               | 15 |

|    | 11.1 | 比较器 INP 输入              | 15 |

| 12 | 实    | E时时钟(RTC)               | 16 |

|    | 12.1 | RTC 预分频                 | 16 |

|    | 12.2 | RTC 亚秒中断                | 16 |

|    | 12.3 | RTC 中断                  | 16 |

|    | 12.4 | RTC 周期性唤醒               | 16 |

|    | 12.5 | RTC 误触发 TISOVF 标志位      | 17 |

| 13 | 低    | 氐功耗定时器(LPTIM)           | 18 |

|    | 13.1 | LPTIM 最大计数值             | 18 |

| 14 | 控    | 空制器局域网(CAN)             | 18 |

|    | 14.1 | CAN 主动错误                | 18 |

| 15 | 芯    | 5片丝印及版本说明               | 19 |

| 16 | 版    | 反本历史                    | 20 |

| 17 | 声    | =明                      | 21 |

|    |      |                         |    |

# 1 勘误列表

表 1-1 勘误概述

| 勘误链接              |                                                                        |                              |    | 芯片版本 |    |    |    |    |  |  |

|-------------------|------------------------------------------------------------------------|------------------------------|----|------|----|----|----|----|--|--|

| 划厌從按              |                                                                        |                              | B版 | C版   | D版 | E版 | G版 | H版 |  |  |

|                   | 章节 2.1: 系统时钟切换                                                         |                              |    |      |    |    |    |    |  |  |

| 章节 2: 电源控制 (PWR)  | 章节 2.2: LP RUN 模式切换到 Stop2 模式                                          |                              |    | •    | •  | •  |    |    |  |  |

|                   | 章节 2.3: 电源掉电后再上电                                                       |                              | •  | •    |    |    |    |    |  |  |

| 章节 3: 复位和时钟控制     | 章节 3.1: 从 Run 模式进入 Stop2 模式                                            |                              | •  | •    | •  | •  | •  | •  |  |  |

| (RCC)             | 章节 3.2: LSE-CSS 故障检测                                                   |                              | •  | •    | •  | •  | •  | •  |  |  |

| 章节 4: GPIO 和 AFIO | 章节 4.1: GPIO                                                           | 模拟功能                         | •  | •    |    |    |    |    |  |  |

|                   | 章节 5.1: ADC 数据左对齐                                                      |                              | •  | •    | •  | •  | •  | •  |  |  |

|                   | 章节 5.2: ADC 注入通道触发规则通道转换                                               |                              |    | •    | •  | •  | •  | •  |  |  |

| 章节 5: 模拟/数字转换     | 章节 5.3: ADC 看门狗                                                        |                              |    | •    | •  | •  | •  | •  |  |  |

| (ADC)             | 章节 5.4: DMA 搬移 ADC 数据                                                  |                              |    | •    | •  | •  | •  | •  |  |  |

|                   | 章节 5.5: 当 ENDC(或 JENDC)标志置位后立即去读取 ADC 数据寄存器 ADC_DAT (或 ADC_JDATx)值异常问题 |                              | •  | •    | •  | •  | •  | •  |  |  |

|                   |                                                                        | 章节 6.1.1: SPI 波特率设置          | •  | •    | •  | •  | •  | •  |  |  |

| 章节 6: 串行外设接口      | 章节 6.1: SPI<br>接口                                                      | 章节 6.1.2: 从模式 CRC<br>校验      | •  | •    | •  | •  | •  | •  |  |  |

| (SPI)             |                                                                        | 章节 6.1.3: SPI CLK GPIO<br>配置 | •  | •    | •  | •  | •  | •  |  |  |

|                   | 章节 6.2: I2S<br>接口                                                      | 章节 6.2.1: PCM 长帧模式           | •  | •    | •  | •  | •  | •  |  |  |

## 国民技术股份有限公司 NSING TECHNOLOGIES INC.

| www.nsingu               |                                        |   |   |   |   |   |   |

|--------------------------|----------------------------------------|---|---|---|---|---|---|

|                          | 章节 7.1: 当前字节传输前必须被管理的软件<br>事件          | • | • | • | • | • | • |

|                          | 章节 7.2: 读单双字节时的注意事项                    | • | • | • | • | • | • |

| 章节7: I2C接口               | 章节 7.3: 与其他外设同时使用 DMA                  | • | • | • | • | • | • |

|                          | 章节 7.4: 异常信号干扰                         | • | • | • | • | • | • |

|                          | 章节 7.5:标准模式下 STOP 建立时间超过最小值限制          | • | • | • | • | • | • |

| 章节 8: 通用同步异步接收           | 章节 8.1: 校验错误标志                         | • | • | • | • | • | • |

| 器(USART)                 | 章节 8.2: RTS 硬件流控                       | • | • | • | • | • | • |

| 章节 9: 调试接口(DBG)          | 章节 9.1: Debug 寄存器                      | • | • | • | • | • | • |

|                          | 章节 10.1: 定时器重复捕获检测                     | • | • | • | • | • | • |

| 章节 10: 定时器(TIM)          | 章节 10.2: 定时器 0%或 100%占空比 PWM<br>输出模式切换 | • | • | • | • | • | • |

| 章节11: 比较器(COMP)          | 章节 11.1: 比较器 INP 输入                    |   | • | • | • | • | • |

|                          | 章节 12.1: RTC 预分频                       | • | • | • | • | • | • |

|                          | 章节 12.2: RTC 亚秒中断                      | • | • | • | • | • | • |

| 章节 12:实时时钟(RTC)          | 章节 12.3: RTC 中断                        | • | • | • | • | • | • |

|                          | 章节 12.4: RTC 周期性唤醒                     | • | • | • | • | • | • |

|                          | 章节 12.3: RTC 误触发 TISOVF 标志位            | • | • | • | • | • | • |

| 章节 13: 低功耗定时器<br>(LPTIM) | 章节 13.1: LPTIM 最大计数值                   | • | • | • | • | • | • |

| 章节 14: 控制器局域网<br>(CAN)   | 章节 14.1: CAN 主动错误                      | • | • | • | • | • |   |

## 2 电源控制 (PWR)

## 2.1 系统时钟切换

## 描述

选择 HSI/HSE 直接作为系统时钟,然后再切换到 MSI 作为系统时钟的过程中,如果此时发生系统复位,可能会导致芯片宕机。

## 解决方法

避免选用 HSI/HSE 直接作为系统时钟,建议选择 PLL 作为系统时钟。

# 2.2LP RUN 模式切换到 Stop2 模式

## 描述

MCU 从 LP RUN 模式切换到 Stop2 模式,唤醒后可能会产生复位。

## 解决方法

进入 Stop2 模式前,确保 PVDBOR 在 Stop2 模式下常开(清除 PWR\_CTRL3 的 PBDTLPR 位为 0),可以解决此问题。

## 2.3 电源掉电后再上电

## 描述

电源掉电,降至600~100mV区间,再重新上电,可能上电不成功。

## 解决方法

MCU 掉电时,需保证芯片 VDD 电压降至 100mV 以下,然后才能给 MCU 上电。

3/19

# 3 复位和时钟控制(RCC)

# 3.1 从 Run 模式进入 Stop2 模式

## 描述

在一定的 AHB CLK 和 APB CLK 分频下, Run 模式极小概率进入不了 Stop2 模式,分频越大可能越容易发生。

## 解决方法

进入 Stop2 模式前,备份 AHB CLK 分频系数,然后配置 AHB CLK 为不分频后,再进入 Stop2 模式,当退出 Stop2 模式时,再恢复原来分频。

## 3.2LSE-CSS 故障检测

## 描述

LSE-CSS 检测到 LSE 停振后,不能通过软件切换到 LSI。

## 解决方法

重新上电。

## 4 GPIO 和 AFIO

## 4.1 GPIO 模拟功能

#### 描述

PA1/PA2/PA3/PA4 这 4 个 GPIO 在输出高电平状态下,切换成模拟功能时,在切换过程中会短暂出现输出电压有 30mv 左右的压降。

## 解决方法

避免上述使用方法。

## 5 模拟/数字转换(ADC)

## 5.1ADC 数据左对齐

#### 描述

ADC 单次转换模式,非 12bit 精度且左对齐情况下,软件触发转换规则通道,ADC\_DAT 寄存器中,无效位的最高位为 1。

## 解决方法

仅保留有效数据位或使用右对齐模式。

## 5.2 ADC 注入通道触发规则通道转换

#### 描述

ADC 连续转换,规则通道外部触发不使能,只软件触发注入通道转换时,规则通道可能会被启动转换,导致 ADC\_DAT 中有数据产生,ADC\_STS 规则通道转换相应的状态位会置起。

5/19

#### 解决方法

忽略规则通道产生的标志位和数据。

## 5.3 ADC 模拟看门狗

#### 描述

ADC 独立工作模式且单次转换且非 12bit 精度时,开启模拟看门狗功能,软件触发转换规则通道/注入通道,模拟看门狗高门限值有效位设置与 ADC 数据寄存器值相等,无效位全 0 时,可能会误触发模拟看门狗。

## 解决方法

此情况下,模拟看门狗高门限值无效位的最高位置1则不触发。

## 5.4 DMA 搬移 ADC 数据

#### 描述

ADC 独立工作模式且连续转换,启动 DMA 搬移 ADC 数据,当搬移完配置的搬移数量,先禁能 DMA,再禁能 ADC,然后继续使能 DMA,在还未使能 ADC 情况下,会出现 DMA 搬移的第一个数据是禁能 DMA 前遗留的 ADC 转换数据。

#### 解决方法

此情况下,如果循环禁能使能 DMA,则在搬移数量 N 基础上增加 1 个数量,首次禁能后,选择读取 DMA 搬移第 1 个~第 N 个数据使用,后续禁能则选择读取 DMA 搬移第 2 个~第 N+1 个数据使用。

# 5.5 当 ENDC(或 JENDC)标志置位后立即去读取 ADC 数据寄存器 ADC DAT (或 ADC JDATx)值异常问题

#### 描述

当规则序列转换完成标志 ENDC (注入序列转换完成标志 JENDC) 置位,立即读 ADC 数据寄存器 ADC\_DAT(ADC\_JDATx),可能读到的是上一次转换的结果。

#### 解决方法

- 1. 在 ADC 规则序列完成标志 ENDC(或注入序列转换完成标志 JENDC)置位后,延时 2 个 ADC\_CLK 时钟再去读 ADC 数据寄存器(ADC\_DAT/ADC\_JDATx);

- 2. 在某些场景,使用任意规则通道完成标志 ENDCA(任意注入通道完成标志 JENDCA)代替 ENDC(JENDCA)标志。

6/19

## 6 串行外设接口(SPI)

## 6.1 SPI 接口

## 6.1.1 SPI 波特率设置

#### 描述

SPI 主模式下, 当设置波特率控制位(BR[2:0])为 fPLCK/2 时, CRC 校验会出错。

#### 解决方法

此情况下,避免设置波特率控制位(BR[2:0])为 fPLCK/2。

## 6.1.2 从模式 CRC 校验

#### 描述

SPI 工作在从模式并且已经使能了 CRC 校验,即使 NSS 引脚为高电平,只要 SPI 接收到时钟信号,仍然会进行 CRC 计算

## 解决方法

在使用 CRC 校验前, 先将 CRC 数据寄存器清空,以便主从设备 CRC 校验保持同步清空步骤如下:

- 1. SPI 使能位复位(置 0)

- 2. CRC 校验位复位(置 0)

- 3. CRC 校验位置位(置1)

- 4. SPI 使能位置位(置1)

## 6.1.3 SPI CLK GPIO 配置

#### 描述

SPI 时钟极性配置为高时,在 SPI 使能后会将 CLK GPIO 拉高后再输出时钟信号。从机有可能会将 这个边沿误判成时钟信号,从而导致从机接收到的数据移位。

#### 解决方法

在 SPI 使能前将 CLK GPIO 根据时钟极性进行配置(时钟极性为高则配置 CLK GPIO 为上拉,时钟极性为低则配置 CLK GPIO 为下拉)

# 6.2**I2S** 接口

## 6.2.1 PCM 长帧模式

## 描述

当 I2S 工作在主模式, PCM 长帧模式, 数据格式为 16bit 扩展到 32bit 或 32bit 时, WS 信号是每 16bit 一个周期而不是 32bit。

## 解决方法

当 I2S 是主模式且必须使用长帧模式时,应当使用 16bit 数据模式。

# 7 I2C接口

## 7.1 当前字节传输前必须被管理的软件事件

#### 描述

在 EV7、EV7\_1、EV6\_1、EV6、EV2、EV8 和 EV3 事件发生时,必须在当前字节传输之前对事件进行处理,否则可能会出现多读一个字节、读取到重复数据或丢失数据的问题。

如果在停止信号生成之前,软件没有读取第 N-1 个数据,则移位寄存器中的第 N 个数据会被损坏(向左移动一位)。

#### 解决方法

- 1. 使用 I2C 传输大于一个字节时,尽量使用 DMA 方式

- 2. 使用 I2C 中断时,将中断优先级调至应用程序的最高优先级

- 3. 当读取数据到达第 N-1 个字节时:

- a) 检测 BSF 为 1

- b) 配置 SCL 为 GPIO 开漏输出,并设为 0

- c) 设置 STOPGEN 为 1

- d) 读取第 N-1 个字节

- e) 配置 SCL 为 I2C 复用功能开漏输出模式

- f) 读取最后一个字节

## 7.2 单次读取单或双字节时的注意事项

#### 描述

在主机读模式,读取的字节长度为单字节和双字节时,可能会出现读取数据错误。

#### 解决方法

- 1. 单字节读取时:

- a) 收到 ADDRF 之后

- b) 设置 ACKEN 位为 0

- c) 清除 ADDRF 位(通过先读 STS1 再读 STS2 清除)

- d) 设置 STOPGEN 为 1

- e) 读取一字节数据。

- 2. 双字节读取时:

- a) 收到 ADDRF 之后

- b) 设置 ACKPOS 位为 1

- c) 清除 ADDRF 位(通过先读 STS1 再读 STS2 清除)

- d) 设置 ACKEN 位为 0

- e) 检测 BSF 位为 1

- f) 设置 STOPGEN 为 1

- g) 连续读取2个字节数据

## 7.3 与其他外设同时使用 DMA

#### 描述

I2C 在使用 DMA 通信期间,如果有别的外设(包括其它组 I2C)也在使用 DMA,会导致 I2C 通信异常。

#### 解决方法

I2C 在使用 DMA 通信期间,关闭其他外设 DMA。

## 7.4 异常信号干扰

#### 描述

I2C 在工作过程,SCL 和 SDA 在通讯过程中可能受到毛刺干扰,造成通讯异常。

#### 解决方法

主机、从机自恢复:

- a) 通过 I2C CTRL1[15](SWRST)位进行 I2C 软复位

- b) 通过控制 RCC 模块内的 RCC APB1RSTR[21]( I2CxRST)位来复位 IIC 模块,完成恢复

- c) 通过调用进行全局软复位 NVIC\_SystemReset()函数来进行全局复位,从而恢复 IIC 模块 主机恢复从机:

- a) 通过控制从机硬件复位管脚复位从机,实现恢复

- b) 通过电源管理机制对从机重新上电,实现恢复

- c) 将 IIC 主机的通讯端口设置为 GPIO 模式,在 SCL 时钟线上发送 9 个 CLOCK 来恢复从机

## 7.5 标准模式下 STOP 建立时间超过最小值限制

## 描述:

主机模式下:通讯速率为 100K 的情况下,触发了从机的时钟延展后,STOP 建立时间会小于 4us。解决方法:

建议根据从机外设时序要求,降低通讯速率到 50K 及以下。

## 8 通用同步异步接收器(USART)

## 8.1校验错误标志

#### 描述

在接收一个字节数据期间,接收到停止位之前,检测到校验错误,校验错误标志位被置起,在此期间,校验错误标志位不能通过软件方式(读状态寄存器,再读数据寄存器)清除。若使能了校验错误中断,会多次进入校验错误中断处理函数。

#### 解决方法

在读数据缓冲区标志位被置起,接收到数据后,再进行清校验错误标志位操作。

若使能了校验错误中断,为避免多次进入中断处理函数,在第一次进入校验错误中断时,关闭校验错误中断,接收到数据后,再重新打开校验错误中断。

## 8.2 RTS 硬件流控

## 描述

使能 RTS 硬件流控,USART 接收一帧数据,当接收到第一个字节数据时,RTS 信号会自动拉高,如果这一个字节数据未及时从数据寄存器中读出,在接收到下一个字节数据后,RTS 信号会重新拉低, USART 重新等待接收下一帧数据。

#### 解决方法

在接收到下一个新数据前,及时将数据从数据寄存器中读出。

# 9 调试接口(DBG)

# 9.1 **Debug** 寄存器

## 描述

$DBGMCU\_IDCODE$  调试寄存器只能在调试模式下被访问(用户程序不能访问),在用户模式下读取返回的值为 0xFF。

## 解决方法

避免在用户应用程序中使用 IDCODE。

## 10 定时器 (TIM)

## 10.1 定时器重复捕获检测

#### 描述

当产生输入捕获时,如果在读取 TIMx\_CCDATx (捕获/比较寄存器 x)期间(读取操作会自动清除捕获标志位)又产生了新的输入捕获, CCxOCF(捕获/比较 x 重复捕获标记)可能仍然会被置位。

#### 解决方法

无

## 10.2 定时器 0%或 100% 占空比 PWM 输出模式切换

#### 描述

TIM 在其他模式(冻结模式除外)切换为 PWM1/2 模式时,如果 PWM 的占空比为 100%或 0%,那 么无法成功切换到 PWM1/2 模式,此时 PWM 占空比修改为非 100%或 0%时可以成功切换到 PWM1/2 模式输出。

#### 解决方法

在强制有效/强制无效/通道匹配有效/通道匹配无效模式切换为 100%或 0%占空比的 PWM1/2 模式时,通过修改 CCxP 实现 100%或 0%占空比。

14 / 19

翻转模式切换为 100%或 0% 占空比的 PWM1/2 模式, 无解决方案。

# 11 比较器 COMP

#### 比较器 INP 输入 11.1

## 描述

PAO/PA1/PA3 作为数字功能引脚且为高电平时,会影响 COMP1 的 INP 输入。

## 解决方法

使用 COMP1 时,不使用 PAO/PA1/PA3 作为数字功能引脚。

## 12 实时时钟(RTC)

## 12.1 RTC 预分频

#### 描述

RTC 异步预分频系数和同步预分频系数不能设置为 0, 否则会导致 RTC 预分频失败。

## 解决方法

避免 RTC 预分频寄存器 TRC\_PRE 的 DIVA[6:0](异步预分频段)和 DIVS[14:0](同步预分频段)设置为 0。

## 12.2 RTC 亚秒中断

## 描述

第一次 RTC 亚秒中断不响应。

## 解决方法

应用程序等待第二次及以后的亚秒中断。

## 12.3 RTC 中断

## 描述

两次 RTC 初始化时间间隔小于 1S,无法产生 RTC 闹钟和周期性唤醒中断。

## 解决方法

应用程初始化RTC时间间隔在1S以上。

## 12.4 RTC 周期性唤醒

## 描述

RTC 周期性唤醒无法作为 Standby 模式的唤醒源。

## 解决方法

选择 RTC 闹钟作为唤醒源。

## 12.5 RTC 误触发 TISOVF 标志位

## 描述

当系统从 STANDBY 模式唤醒,或者 IWDG 超时产生系统复位时,RTC 会概率性误触发 TISOVF 标志位。

## 解决方法

在进入 STANDBY 模式或者 IWDG 超时之前,当 SHOPF 标志位为 0 时,配置一次 RTC\_SCTRL.SUBF[14:0]寄存器,该标志会被置 1。等到 SHOPF 标志位再次为 0 时,第二次配置 RTC\_SCTRL.SUBF[14:0]寄存器即可,注意在软件执行上述过程中不可以触发 NRST。

## 13 低功耗定时器(LPTIM)

## 13.1 LPTIM 最大计数值

## 描述

LPTIM 时钟源选择内部时钟源(LPTIM\_CFG 寄存器 CKSLE 位为 0),且计数器配置为 Input1 上的每个有效钟脉冲递增(LPTIM\_CFG 寄存器 CNTMEN 位为 1),计数器最大计数值为 ARRVAL(自动重装载计数器)-1。

## 解决方法

LPTIM\_CFG 寄存器 CKSLE 位为 0,且 LPTIM\_CFG 寄存器 CNTMEN 位为 1 时,需将计算的 ARRVAL 目标值加 1 配置使用

## 14 控制器局域网(CAN)

## 14.1 CAN 主动错误

#### 描述

CAN 处于正常模式下, CAN bit 位硬同步后如果总线其它节点的波特率偏差过大(接近或者超过同步段),则 CAN 模块容易报主动错误。

#### 解决方法

无

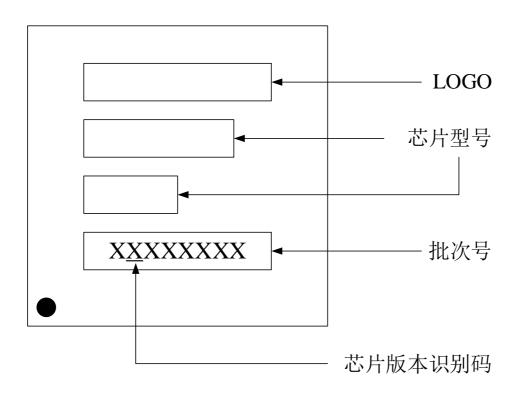

# 15 芯片丝印及版本说明

# 16 版本历史

| 日期         | 版本     | 修改                                                                                                                    |

|------------|--------|-----------------------------------------------------------------------------------------------------------------------|

| 2021.09.15 | V1.0.0 | 初始版本                                                                                                                  |

| 2021.11.30 | V1.0.1 | 新增 5.3 ADC 模拟看门狗<br>新增 5.4 DMA 搬移 ADC 数据<br>新增 7.4 异常信号干扰<br>新增 12.2 RTC 亚秒中断                                         |

| 2022.02.22 | V1.1.0 | 新增 6.1.3 SPI CLK GPIO 配置                                                                                              |

| 2022.04.06 | V1.2   | 修改表 1-1 勘误描述增加 E 版本 修改 12.2 章节将 RTC 亚皮秒改成 RTC 亚秒 增加 13 章节低功耗定时器(LPTIM) 增加 3.2 LSE-CSS 故障检测章节 修改 7.3 章节增加 I2C DMA 使用限制 |

| 2022.08.31 | V1.2.1 | 增加 14 章节控制器局域网(CAN)<br>增加 12.3 RTC 中断章节<br>增加 12.4 RTC 周期性唤醒章节                                                        |

| 2023.02.14 | V1.3   | 增加 12.5 章节 RTC 误触发 TISOVF 标志位                                                                                         |

| 2024.07.18 | V2.0.0 | 增加 5.5 当 ENDC(或 JENDC)标志置位后立即去读取 ADC 数据寄存器 ADC_DAT (或 ADC_JDATx)值异常问题章节                                               |

| 2025.09.28 | V2.1.0 | 增加 7.5 标准模式下 STOP 建立时间超过最小值限制章节增加 10.2 定时器 0%或 100%占空比 PWM 输出模式切换章节                                                   |

## 17 声明

国民技术股份有限公司(下称"国民技术")对此文档拥有专属产权。依据中华人民共和国的 法律、条约以及世界其他法域相适用的管辖,此文档及其中描述的国民技术产品(下称"产 品")为公司所有。

国民技术在此并未授予专利权、著作权、商标权或其他任何知识产权许可。所提到或引用的 第三方名称或品牌(如有)仅用作区别之目的。

国民技术保留随时变更、订正、增强、修改和改良此文档的权利,恕不另行通知。请使用人 在下单购买前联系国民技术获取此文档的最新版本。

国民技术竭力提供准确可信的资讯,但即便如此,并不推定国民技术对此文档准确性和可靠 性承担责任。

使用此文档信息以及生成产品时,使用者应当进行合理的设计、编程并测试其功能性和安全 性,国民技术不对任何因使用此文档或本产品而产生的任何直接、间接、意外、特殊、惩罚 性或衍生性损害结果承担责任。

国民技术对于产品在系统或设备中的应用效果没有任何故意或保证, 如有任何应用在其发生 操作不当或故障情况下,有可能致使人员伤亡、人身伤害或严重财产损失,则此类应用被视 为"不安全使用"。

不安全使用包括但不限于:外科手术设备、原子能控制仪器、飞机或宇宙飞船仪器、所有类 型的安全装置以及其他旨在支持或维持生命的应用。

所有不安全使用的风险应由使用人承担,同时使用人应使国民技术免于因为这类不安全使用 而导致被诉、支付费用、发生损害或承担责任时的赔偿。

对于此文档和产品的任何明示、默示之保证,包括但不限于适销性、特定用途适用性和不侵 权的保证责任,国民技术可在法律允许范围内进行免责。

未经明确许可,任何人不得以任何理由对此文档的全部或部分进行使用、复制、修改、抄录 和传播。