N32G430 Series Errata Sheet V1.4.0

# **Contents**

|     | Erra                                   | Errata List                                                                                                    |                     |  |  |  |

|-----|----------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------|--|--|--|

|     | Powe                                   | er Control (PWR)                                                                                               | 3                   |  |  |  |

| 2.1 | 1                                      | Cannot reset from DEBUG STOP2 mode by pressing NRST button                                                     | 3                   |  |  |  |

|     | Time                                   | or (TIM)                                                                                                       | 4                   |  |  |  |

| 3.1 | 1                                      | TIM1/2/3/4/5/8 cannot generate compare events under certain circumstances                                      | 4                   |  |  |  |

| 3.2 | 2                                      | The issue of switching from another mode to 100% or 0% duty cycle PWM mode                                     | 4                   |  |  |  |

|     | Seria                                  |                                                                                                                |                     |  |  |  |

| 4.1 |                                        |                                                                                                                |                     |  |  |  |

|     |                                        |                                                                                                                |                     |  |  |  |

|     |                                        |                                                                                                                |                     |  |  |  |

| 5 1 |                                        |                                                                                                                |                     |  |  |  |

|     |                                        |                                                                                                                |                     |  |  |  |

|     |                                        |                                                                                                                |                     |  |  |  |

|     |                                        |                                                                                                                |                     |  |  |  |

|     |                                        |                                                                                                                |                     |  |  |  |

| 5.5 | 5                                      | ·                                                                                                              |                     |  |  |  |

| 5.6 | 6                                      | RTC_DATE register lock                                                                                         | 7                   |  |  |  |

|     | GPIC                                   | O and AFIO                                                                                                     | 8                   |  |  |  |

| 6.1 | 1                                      | IO appeared burr during power-on                                                                               | 8                   |  |  |  |

|     | Cont                                   | roller Area Network (CAN)                                                                                      | 9                   |  |  |  |

| 7.1 | 1                                      | CAN active error                                                                                               | 9                   |  |  |  |

|     | I2C i                                  | nterface                                                                                                       | 10                  |  |  |  |

| 8.1 | 1                                      | STOP establishment time exceeds minimum threshold in standard mode                                             | 10                  |  |  |  |

|     | Marl                                   | king information                                                                                               | 11                  |  |  |  |

| )   |                                        |                                                                                                                |                     |  |  |  |

|     |                                        | ·                                                                                                              |                     |  |  |  |

|     | 3. 3. 3. 3. 3. 3. 5. 5. 5. 5. 6. 7. 8. | Power 2.1  Time 3.1  3.2  Seria 4.1  4.1.1  Real 5.1  5.2  5.3  5.4  5.5  6.1  Cont 7.1  I2C i 8.1  Marl Versi | Power Control (PWR) |  |  |  |

# 1 Errata List

**Table 1-1 Errata overview**

|                                              | Errata link                                                                                      |                                    |   | Chip version |  |

|----------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------|---|--------------|--|

|                                              | Version C                                                                                        | Version D                          |   |              |  |

| Section 2: Power Control (PWR)               | Section 2.1: Cannot reset from DEBUG STOP2 mode by pressing NRST button                          |                                    | • |              |  |

| Section 3: Timer (TIM)                       | Section 3.1: TIM1/2/3/4/5/8 cannot generate compare events under certain circumstances           |                                    | • | •            |  |

| Section 3. Timer (Thvi)                      | Section 3.2: The issue of switching from another mode to 100% or 0% duty cycle PWM mode          |                                    | • | •            |  |

| Section 4: Serial Peripheral Interface (SPI) | Section 4.1: I2S interface                                                                       | Section 4.1.1: PCM long frame mode | • | •            |  |

|                                              | Section 5.1: RTC automatic wake up                                                               |                                    | • | •            |  |

|                                              | Section 5.2: The RTC wakeup event is generated before the chip enters STANDBY and cannot wake up |                                    | • |              |  |

|                                              | Section 5.3: The RTC caler initialized multiple times w                                          |                                    | • |              |  |

| Section 5: Real Time Clock (RTC)             | Section 5.4: The RTC trigg                                                                       | ers the TISOVF flag by             | • |              |  |

|                                              | Section 5.5: The shift opera subsecond causes the curre inaccurate                               |                                    | • | •            |  |

|                                              | Section 5.6: RTC_DATE register lock                                                              |                                    | • | •            |  |

| Section 6: GPIO and AFIO                     | Section 6: GPIO and AFIO Section 6.1: IO appeared burr dur                                       |                                    | • |              |  |

| Section 7: Controller Area Network(CAN)      | Section 7.1: CAN active en                                                                       | ror                                | • |              |  |

| Section 8: I2C interface | Section 8.1: STOP establishment time exceeds minimum threshold in standard mode | • | • |

|--------------------------|---------------------------------------------------------------------------------|---|---|

|--------------------------|---------------------------------------------------------------------------------|---|---|

# 2 Power Control (PWR)

# 2.1 Cannot reset from DEBUG STOP2 mode by pressing NRST button

#### Description

When the DBG\_CTRL.STOP bit is set to 1 and the chip enters the STOP2 mode, the chip cannot be reset by pressing the NRST button.

#### Resolution

Before the chip enters STOP2 mode, clear the DBG\_CTRL.STOP bit to 0.

### 3 Timer (TIM)

### 3.1 TIM1/2/3/4/5/8 cannot generate compare events under certain

#### circumstances

#### Description

In edge-aligned mode, in up-counting PWM1 mode, when the current PWM cycle CCDATx shadow register >= AR value, the shadow register value of CCDATx in the next PWM cycle is 0. At the moment when the PWM cycle counter is 0, although the count value = CCDATx shadow register value = 0 and OCxREF = 0, but still no compare event is generated.

#### Resolution

If it is not required that "the comparison event is generated at the time when the count value = the shadow register of the comparison value =0", the comparison event generated through another channel can replace the comparison event that is not generated.

# 3.2 The issue of switching from another mode to 100% or 0% duty cycle

#### PWM mode

#### **Description**

When switching from any mode (except frozen mode) to PWM1/2 mode, if the PWM duty cycle is set to 100% or 0%, the mode switch to PWM1/2 mode fail, if reconfig the PWM duty (not 0% or 100%), the mode switch to PWM1/2 mode success.

#### Workaround

When switching from forced active/forced inactive/set channel x to the active level on match/ set channel x to the inactive level on match mode to PWM1/2 mode with a 100% or 0% duty cycle, modify CCxP to achive the PWM with 100% or 0% duty.

When switching from toggle mode to PWM1/2 mode with a 100% or 0% duty cycle, have no solution.

# 4 Serial Peripheral Interface (SPI)

### 4.1 I2S interface

# 4.1.1 PCM long frame mode

#### Description

When I2S works in master mode, PCM long frame mode, and the data format is "32bit" or "16bit extended to 32bit", the WS signal is one cycle per 16bit instead of 32bit.

#### Resolution

When I2S works in master mode and the long frame mode must be used, the 16bit data mode should be used.

# 5 Real Time Clock (RTC)

### 5.1 RTC automatic wake up

#### Description

After the RTC calendar setting is completed, configure the automatic wake-up function. The time from enabling automatic wake-up to the first wake-up is smaller than the wake-up automatic reload value, and the subsequent automatic wake-up time is normal.

#### Resolution

Ignore the first wakeup.

# 5.2 The RTC wakeup event is generated before the chip enters STANDBY and cannot wake up

#### Description

Before the chip enters STANDBY mode, if an RTC wakeup event occurs, the chip will not wake up after entering STANDBY mode.

#### Resolution

None.

# 5.3 The RTC calendar function cannot be initialized multiple times within

#### 1 second

#### Description

The RTC calendar function is initialized multiple times within 1 second, so that the RTC alarm clock interrupt cannot be generated.

#### Resolution

The interval between two initializations of the RTC calendar function is more than 1 second.

# 5.4 The RTC triggers the TISOVF flag by mistake

#### Description

When the system wakes up from STANDBY mode or the IWDG times out and the system reset, the RTC may triggers the TISOVF flag by mistake probability.

#### Resolution

Before entering STANDBY mode or IWDG time out, when the SHOPF flag is 0, configure

RTC\_SCTRL.SUBF[14:0] register for the first time, and SHOPF flag will set 1. When SHOPF flag is 0 again, configure RTC\_SCTRL.SUBF[14:0] register for the second time. Note that NRST cannot be triggered during above process.

### 5.5 The shift operation of the RTC on the subsecond causes the current

### wake-up time is inaccurate

#### Description

When the RTC is configured to periodic wake up, performing the shift operation for subseconds before triggering the periodic wake-up will cause the current wake-up time is inaccurate, and the subsequent wake-up time will be normal.

#### Resolution

None

# 5.6 RTC DATE register lock

#### Description

- Before the system software reset, the RTC\_DATE register is not read after reading the RTC\_SUBS or RTC\_TSH shadow register, and the RTC\_DATE register will restores the default value after the system software resets and initializes the RTC without configuration or reads the RTC\_DATE register;

- 2. When reading the calendar, after reading the RTC\_SUBS or RTC\_TSH shadow register, the value of the RTC\_DATE register remains unchanged;

#### Resolution

- 1. Read the RTC DATE register before initializing the RTC;

- 2. After reading the RTC\_SUBS or RTC\_TSH shadow register, read the RTC\_DATE register;

# 6 GPIO and AFIO

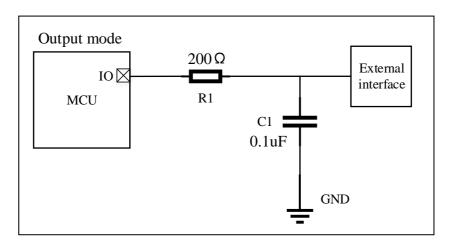

# 6.1 **IO appeared burr during power-on**

#### Description

When the MCU is powered on, some IOs will have burrs appeared.

#### Resolution

When IO is used as input, the burr has no effect on MCU; When IO is used as output, 2000hm resistor and 0.1uF capacitor are applied for filtering.

# 7 Controller Area Network (CAN)

### 7.1 CAN active error

#### Description

When the CAN is in normal mode and the CAN bit is hard synchronized, if the baud rate deviation of other nodes is too large(approaching or exceeding the synchronization segment), the CAN module is prone to generate the active error.

#### Workaround

D version chip solution

# 8 I2C interface

# 8.1 STOP establishment time exceeds minimum threshold in standard

### Description

mode

In master mode: At a communication rate of 100K, triggering the slave's clock extension results in a STOP establishment time less than  $4\mu s$ .

#### Workaround

Recommend reducing the communication rate to 50K or below based on the slave peripheral's timing requirements.

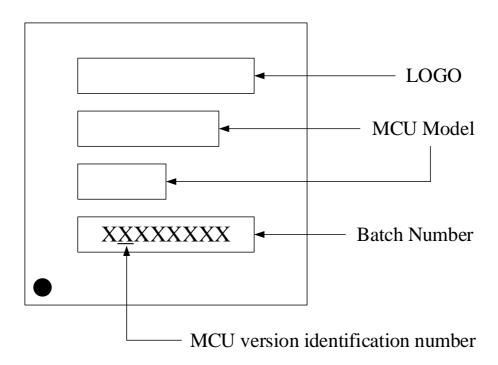

# 9 Marking information

# 10 Version history

| Date       | Version | Remark                                                                                                                                                                                                                                                                                                              |  |  |

|------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 2022.5.12  | V1.0    | Initial release                                                                                                                                                                                                                                                                                                     |  |  |

| 2022.7.19  | V1.1    | Add section 6                                                                                                                                                                                                                                                                                                       |  |  |

| 2023.3.21  | V1.2.0  | <ol> <li>Add section 7, CAN active error</li> <li>Modify section 5.2, wakeup event instead of tamper event</li> <li>Add section 5.4, The RTC triggers the TISOVF flag by mistake</li> <li>Add section 5.5, The shift operation of the RTC on the subsecond causes the current wake-up time is inaccurate</li> </ol> |  |  |

| 2023.5.9   | V1.3.0  | 1. Add chapter 5.6                                                                                                                                                                                                                                                                                                  |  |  |

| 2025.09.18 | V1.4.0  | <ol> <li>Modify header and footer</li> <li>Add chapter 3.2</li> <li>Add chapter 8</li> </ol>                                                                                                                                                                                                                        |  |  |

### 11 Notice

This document is the exclusive property of NSING TECHNOLOGIES PTE. LTD. (Hereinafter referred to as NSING). This document, and the product of NSING described herein (Hereinafter referred to as the Product) are owned by NSING under the laws and treaties of Republic of Singapore and other applicable jurisdictions worldwide. The intellectual properties of the product belong to NSING Technologies Inc. and NSING Technologies Inc. does not grant any third party any license under its patents, copyrights, trademarks, or other intellectual property rights. Names and brands of third party may be mentioned or referred thereto (if any) for identification purposes only. NSING reserves the right to make changes, corrections, enhancements, modifications, and improvements to this document at any time without notice. Please contact NSING and obtain the latest version of this document before placing orders. Although NSING has attempted to provide accurate and reliable information, NSING assumes no responsibility for the accuracy and reliability of this document. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. In no event shall NSING be liable for any direct, indirect, incidental, special, exemplary, or consequential damages arising in any way out of the use of this document or the Product. NSING Products are neither intended nor warranted for usage in systems or equipment, any malfunction or failure of which may cause loss of human life, bodily injury or severe property damage. Such applications are deemed, Insecure Usage'. Insecure usage includes, but is not limited to: equipment for surgical implementation, atomic energy control instruments, airplane or spaceship instruments, all types of safety devices, and other applications intended to supporter sustain life. All Insecure Usage shall be made at user's risk. User shall indemnify NSING and hold NSING harmless from and against all claims, costs, damages, and other liabilities, arising from or related to any customer's Insecure Usage Any express or implied warranty with regard to this document or the Product, including, but not limited to. The warranties of merchantability, fitness for a particular purpose and non-infringement are disclaimed to the fullest extent permitted by law. Unless otherwise explicitly permitted by NSING, anyone may not use, duplicate, modify, transcribe or otherwise distribute this document for any purposes, in whole or in part.