# N32WB03x Bluetooth® Low Energy wireless SoC Family

#### **Datasheet**

N32WB03x series use 32-bit ARM Cortex-M0 core, support BLE 5.1 and SIG Mesh, and feature a frequency up to 64 MHz, 4.2 mA radio transmit current, 3.8 mA radio receive current, +6 dBm maximum transmitting power, and -96 dBm @BLE 1 Mbps RX sensitivity.

# **Key Features**

- CPU Core

- ➤ 32-bit ARM Cortex-M0 core

- > Frequency up to 64 MHz

- Storage

- > 256/512 KB Flash

- ➤ 64 KB SRAM

- Power Dissipation

- > Radio receive current: 3.8 mA@3.3 V

- Radio transmit current: 4.2 mA @0 dBm/3.3 V

- > Sleep mode (48 KB RAM retention): 1.4 μA@3 V

- PD mode: 130 nA

#### RF Specification

- > RX sensitivity: -96 dBm @BLE 1 Mbps

- RX sensitivity: -93 dBm @BLE 2 Mbps

- ➤ Power of programmable transmitter: up to +6 dBm

- > Single end antenna

#### Clock

- ➤ HSE: 32 MHz high speed external crystal

- LSE: 32.768 KHz low speed external crystal

- > HSI: high speed internal RC 64 MHz

- LSI: low speed internal RC 32 KHz

- > Support one clock output; different clock output can be configured; clock can be output after divided by four.

#### Reset

- > Power-on/off/external pin reset

- Watchdog reset

#### • Communications Interface

- > 2 × USART interfaces, with rate up to 4 Mbps (configurable as ISO7816, IrDA, LIN)

- ➤ 1 × LPUART interface, featuring low-power dissipation, supporting communication rate up to 9,600 bps and low-power wakeup in Sleep mode

- > 2 × SPI interfaces, with rate up to 16 MHz, master/slave configurable, supporting I2S

- ➤ 1 × I2C interface, with rate up to 1 MHz, master/slave configurable

#### Counter

- ➤ 1 × 16-bit advanced counter, supporting functions like input capture, output compare, PWM output, and quadrature encoder input; 4 independent channels, 3 of which support 6 complementary PWM outputs

- > 1 × 16-bit general-purpose counter, supporting functions like input capture, output compare, PWM output, and mono-pulse output, with 4 independent channels

- ➤ 1 × 16-bit basic counter

- $\triangleright$  1 × 24-bit system timer

- ➤ 1 × 7-bit window watchdog (WWDG)

- ➤ 1 × 12-bit independent watchdog (IWDG)

#### Analog Interface

- ➤ 1 × 10-bit 1.33 Msps ADC, supporting 5 external single-ended channels, 1 differential MIC channel, 2 internal channels

- ➤ Built-in PGA up to 128x

- MIC BIAS voltage, adjustable between 1.6 V and 2.3 V

- 21 × GPIO, supporting multiplexing

- 1 × high speed 5-channel DMA controller

- 1 × IR transmission controller, supporting all infrared remote control protocols

0

- 1 × KEYSCAN module, where 8/10/13 GPIOs support 44/65/104 key functions respectively

- RTC real-time clock, supporting perpetual calendar (that can identify leap years), alarm events, and periodic wakeup

- Support hardware CRC16 and CRC32 operations

- Operating Conditions

➤ Operating voltage: 1.8V/2.32 V~3.6 V

➤ Operating temperature: -40°C~85°C/105°C

➤ ESD: ±2 KV (HBM)

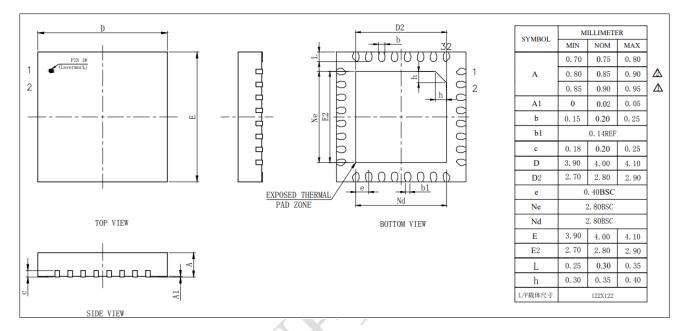

#### Encapsulation

➤ QFN32 (4 mm × 4 mm)

#### • Ordering information

| Series   | Part Number    |

|----------|----------------|

| N32WB03x | N32WB031KCQ6-1 |

|          | N32WB031KEQ6-2 |

|          | N32WB031KEQ6-1 |

|          | N32WB031KEQ7-1 |

# Contents

| 1 | OVI            | ERVIEW                                                          | 9   |

|---|----------------|-----------------------------------------------------------------|-----|

|   | 1.1            | Naming Rule                                                     | 10  |

|   | 1.2            | DEVICE SCHEDULE                                                 | 10  |

| 2 | PRO            | DDUCTION FEATURES                                               | 12  |

|   | 2.1            | PROCESSOR CORE                                                  | \10 |

|   | 2.2            | MEMORY                                                          | 12  |

|   | 2.2.           |                                                                 |     |

|   | 2.2.2          |                                                                 | 12  |

|   | 2.3            | Low Power Modes                                                 | 12  |

|   | 2.4            | CLOCK SYSTEM                                                    |     |

|   | 2.5            | GENERAL PURPOSE INPUT/OUTPUT (GPIO).                            | 14  |

|   | 2.6            | EXTI                                                            | 15  |

|   | 2.7            | DMA                                                             | 15  |

|   | 2.8            | CRC                                                             | 15  |

|   | 2.9            | TIMER AND WATCHDOG                                              |     |

|   | 2.9.           | Basic Timer (TIM6)                                              | 16  |

|   | 2.9.2          |                                                                 | 16  |

|   | 2.9.3          | 3 Advanced Timer (TIM1)<br>4 System Tick Timer (Systick)        | 17  |

|   | 2.9.4<br>2.9.5 |                                                                 | 18  |

|   | 2.10           | ADC                                                             |     |

|   | 2.11           | I2C Bus Interface (I2C)                                         |     |

|   | 2.12           | Universal Synchronous/Asynchronous Receiver/Transmitter (USART) |     |

|   | 2.13           | SERIAL PERIPHERAL INTERFACE (SPI)                               |     |

|   | 2.14           | SERIAL AUDIO PORT (I2S)                                         |     |

|   | 2.15           | REAL TIME CLOCK (RTC)                                           |     |

|   | 2.16           | INFRARED CONTROLLER (IRC)                                       |     |

|   | 2.17           | AUTOMATIC KEY SCANNING (KEYSCAN)                                |     |

|   | 2.18           | SERIAL SWD DEBUGGING INTERFACE (SWD)                            |     |

|   |                |                                                                 |     |

| 3 | DEI            | FINITION AND DESCRIPTION                                        |     |

|   | 3.1            | ENCAPSULATION DIAGRAM                                           |     |

|   | 3.1.           |                                                                 |     |

|   | 3.2            | DEFINITION OF PIN MULTIPLEXING                                  | 28  |

| 4 | ELF            | CCTRICAL CHARACTERISTICS                                        | 31  |

|   | 4.1            | TEST CONDITION                                                  | 31  |

|   | 4.1.           |                                                                 |     |

|   | 4.1.2          |                                                                 |     |

|   | 4.1.3<br>4.1.4 | **                                                              |     |

|   | 4.1.           | 1                                                               |     |

|   | 4.1.0          | 5 Power Supply Plan                                             | 32  |

|   | 4.1.           | 7 Current Consumption Measurement                               | 33  |

|   | 4.2 A  | BSOLUTE MAXIMUM RATING                                     | 34 |

|---|--------|------------------------------------------------------------|----|

|   | 4.3 C  | PERATING CONDITIONS                                        | 35 |

|   | 4.3.1  | General Operating Conditions                               |    |

|   | 4.3.2  | Power-on and Power-off Operating Conditions                |    |

|   | 4.3.3  | Characteristics of Built-in Reset and Power Control Module |    |

|   | 4.3.4  | Characteristics of DCDC                                    |    |

|   | 4.3.5  | Characteristics of Supply Current                          | 37 |

|   | 4.3.6  | Characteristics of External Clock Source                   | 38 |

|   | 4.3.7  | Characteristics of Internal Clock Source                   | 40 |

|   | 4.3.8  | Time Required to Wake Up from Low Power Modes              | 41 |

|   | 4.3.9  | Characteristics of FLASH Memory                            | 42 |

|   | 4.3.10 | Absolute Maximum (Electrical Sensitivity)                  | 42 |

|   | 4.3.11 | I/O port characteristics                                   |    |

|   | 4.3.12 | Characteristics of NRST Pins                               |    |

|   | 4.3.13 | Characteristics of TIM Timer                               | 47 |

|   | 4.3.14 | Characteristics of I2C Interface                           |    |

|   | 4.3.15 | Characteristics of SPI                                     |    |

|   | 4.3.16 | Characteristics of Temperature Sensor (TS)                 | 53 |

|   | 4.3.17 | Characteristics of ADC                                     |    |

|   | 4.3.18 | Characteristics of PGA                                     |    |

|   | 4.3.19 | Characteristics of KEYSCAN                                 |    |

|   | 4.3.20 | Characteristics of BLE                                     | 56 |

| 5 | ENCA   | PSULATION SIZE                                             | 58 |

|   |        | FN32                                                       |    |

|   |        |                                                            |    |

| 6 | VERS   | ION HISTORY                                                | 59 |

| _ |        |                                                            | 60 |

| , | NOTI   |                                                            | 60 |

# List of Tables

| Table 1-1 Resource Configuration of N32WB03x Series                                       | 10 |

|-------------------------------------------------------------------------------------------|----|

| Table 3-1 Definition of Pin                                                               | 28 |

| Table 4-1 Voltage Characteristics                                                         | 34 |

| Table 4-2 Current Characteristics                                                         | 34 |

| Table 4-3 Temperature Characteristics                                                     | 35 |

| Table 4-4 General Operating Conditions                                                    | 35 |

| Table 4-5 Power-on and Power-off Operating Conditions                                     | 35 |

| Table 4-6 Characteristics of Built-in Reset and Power Control Module <sup>(1)</sup>       | 36 |

| Table 4-7 Built-in DCDC Power Management                                                  | 36 |

| Table 4-8 Typical Current Consumption in Sleep Mode <sup>(1)</sup>                        | 37 |

| Table 4-9 Typical Current Consumption in Operating Mode                                   | 37 |

| Table 4-10 BLE Power Dissipation                                                          |    |

| Table 4-11 Characteristics of HSE 32 MHz Oscillator <sup>(1)(2)</sup>                     | 38 |

| Table 4-12 Characteristics of LSE Oscillator (f <sub>LSE</sub> =32.768kHz) <sup>(1)</sup> | 39 |

| Table 4-13 Characteristics of HSI Oscillator <sup>(1)(2)</sup>                            | 40 |

| Table 4-14 Characteristics of LSI Oscillator <sup>(1)</sup>                               | 41 |

| Table 4-15 Time Required to Wake Up from Low Power Modes                                  | 41 |

| Table 4-16 Characteristics of Memory                                                      | 42 |

| Table 4-17 Flash Memory Life and Data Retention Period                                    | 42 |

| Table 4-18 Absolute Maximum of ESD                                                        | 42 |

| Table 4-19 Electrical Sensitivity                                                         | 43 |

| Table 4-20 Static Characteristics of I/O <sup>(1)(2)</sup>                                | 43 |

| Table 4-21 I/O Output Voltage                                                             | 44 |

| Table 4-22 Input and Output AC Characteristics <sup>(1)</sup>                             | 44 |

| Table 4-23 Characteristics of NRST Pins                                                   | 46 |

| Table 4-24 Characteristics of TIMx <sup>(1)(2)</sup>                                      | 47 |

| Table 4-25 Characteristics of I2C Interface <sup>(1)</sup>                                | 49 |

| Table 4-26 Characteristics of SPI <sup>(1)</sup>                                          | 50 |

| Table 4-27 Characteristics of Temperature Sensor                                          | 53 |

| Table 4-28 Characteristics of ADC                                                         | 54 |

| Table 4-29 Characteristics of PGA                          | 55 |

|------------------------------------------------------------|----|

| Table 4-30 Characteristics of KEYSCAN                      | 55 |

|                                                            |    |

| Table 4-31 BLE Receiving Characteristics <sup>(1)</sup>    |    |

| Table 4-32 BLE Transmitting Characteristics <sup>(1)</sup> | 56 |

# List of Figures

| Figure 1-1 Block Diagram of N32WB03x Series                            | 9  |

|------------------------------------------------------------------------|----|

| Figure 1-2 Structure of N32WB03x Series Ordering Code                  | 10 |

| Figure 2-1 Memory Mapping                                              | 12 |

| Figure 2-2 Clock Tree                                                  | 14 |

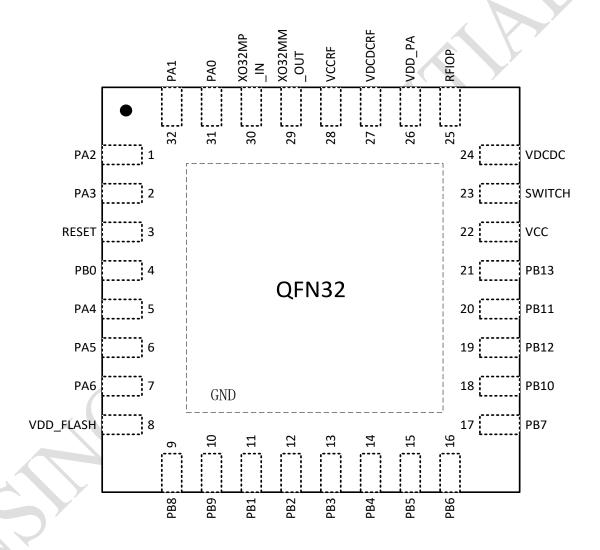

| Figure 3-1 QFN32 Pin Distribution of N32WB03x Series                   | 27 |

| Figure 4-1 Load Conditions for Pins                                    | 31 |

| Figure 4-2 Input Voltage of Pin                                        | 32 |

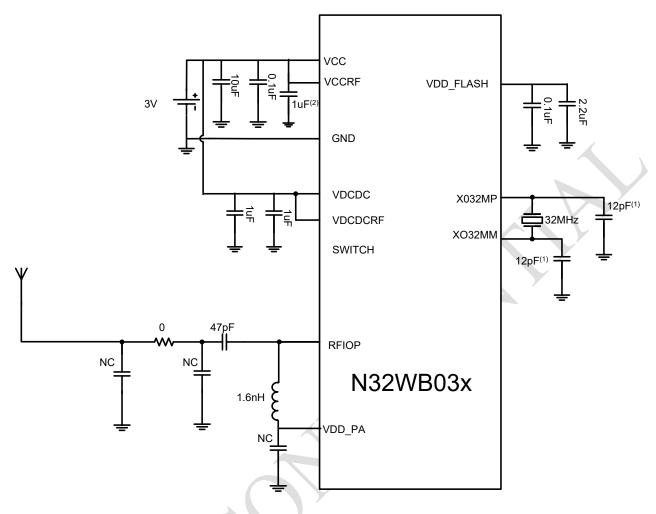

| Figure 4-3 Power Supply Plan                                           | 32 |

| Figure 4-4 Current Consumption Measurement Plan                        | 33 |

| Figure 4-5 Typical Application with a 32 MHz Crystal                   | 39 |

| Figure 4-6 Typical Application with a 32.768 kH Crystal                | 40 |

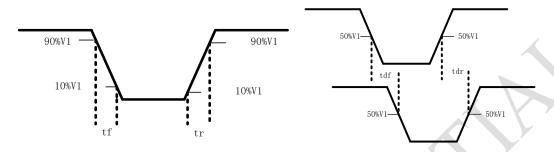

| Figure 4-7 Definition of Input and Output AC Characteristics           |    |

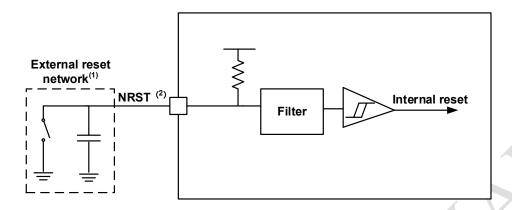

| Figure 4-8 Recommended NRST Pin Protection                             | 46 |

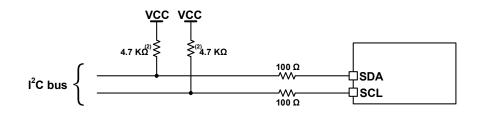

| Figure 4-9 AC Waveform and Measuring Circuit of I2C Bus <sup>(1)</sup> | 50 |

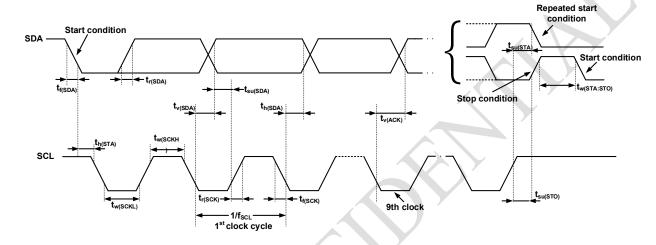

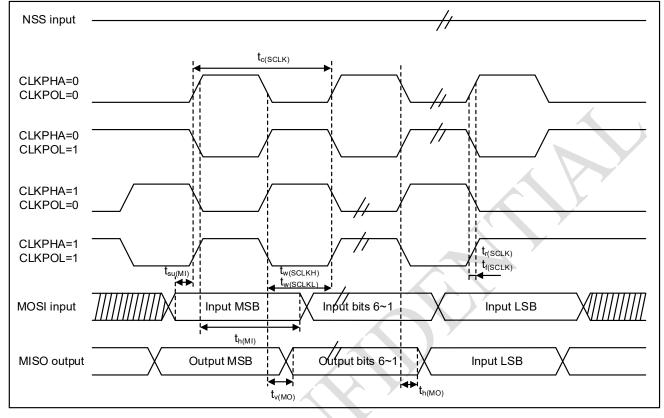

| Figure 4-10 SPI Sequence Diagram–Slave Mode and CPHA=0                 | 52 |

| Figure 4-11 SPI Sequence Diagram–Slave Mode and CPHA=1 <sup>(1)</sup>  | 52 |

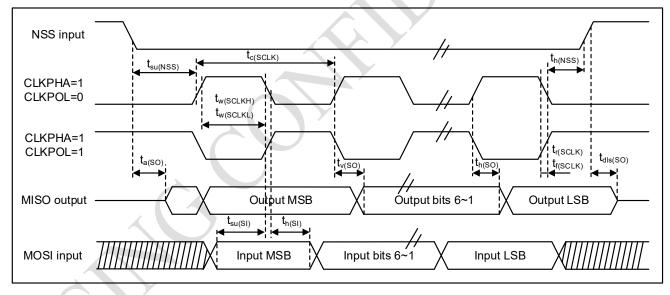

| Figure 4-12 SPI Sequence Diagram–Master Mode <sup>(1)</sup>            | 53 |

| Figure 5-1 OFN32 Encapsulation Size                                    | 58 |

#### 1 Overview

N32WB03x Bluetooth® Low Energy wireless SoC Family is Nations' next generation of high performance, ultra-low power dissipation chips that support BLE 5.1. Equipped with 32-bit ARM Cortex®-M0 core, it features a frequency up to 64 MHz, 64 KB SRAM integrated on the chip, and 256/512 KB Flash.

Integrated with an advanced BLE 5.1 RF transceiver, it is compliant with the BLE 5.1 standard and provided with multiple modes including standard 1 Mbps BLE mode, enhanced 2 Mbps BLE mode. In the 1 Mbps or 2 Mbps BLE mode, it supports RSSI, master/slave role, multi-connection, packet length expansion, KEYSCAN, IRC, 10-bit 1.33 Msps ADC, analog MIC input, PGA, basic, universal and advanced timers, RTC, WWDG, IWDG, LPUART, USART, SPI, I2C, and other peripherals.

It is applicable to many application scenarios including Bluetooth KEY, OBU, data transmission module, Bluetooth voice remote controller, and smart home.

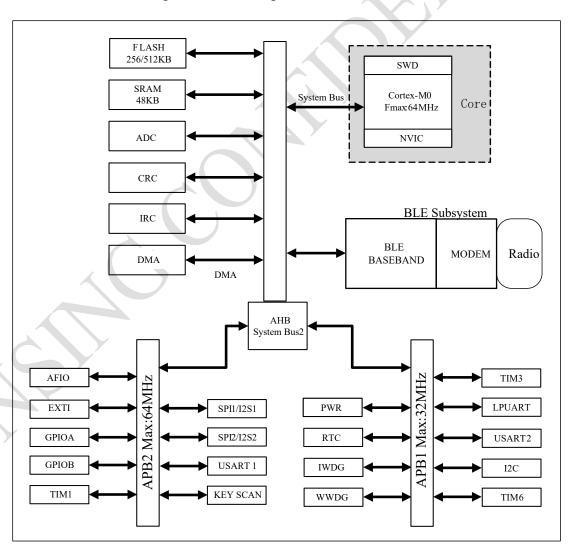

Figure 1-1 shows the block diagram of N32WB03x series.

Figure 1-1 Block Diagram of N32WB03x Series

## 1.1 Naming Rule

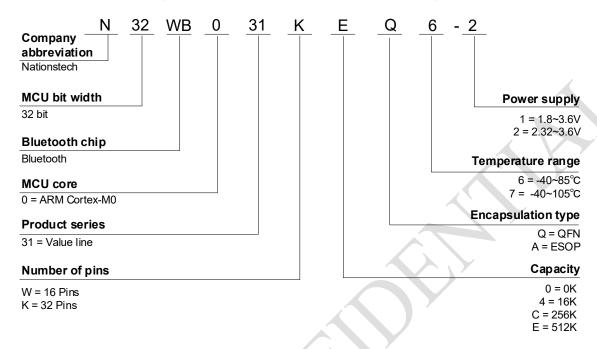

Figure 1-2 Structure of N32WB03x Series Ordering Code

# **1.2** Device Schedule

Table 1-1 Resource Configuration of N32WB03x Series

|                            | N32WB031KEQ6-2 N32WB031KEQ6-1 N32WB031KEQ7-1 N32WB03                           |                                                                                                 |                       | N32WB031KCQ6-1       |  |  |  |

|----------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----------------------|----------------------|--|--|--|

| ol                         | BLE5.1                                                                         |                                                                                                 |                       |                      |  |  |  |

| KB)                        |                                                                                | 512                                                                                             |                       | 256                  |  |  |  |

| (KB)                       |                                                                                | $\epsilon$                                                                                      | 54                    |                      |  |  |  |

|                            |                                                                                | ARM Cortex-                                                                                     | -M0 @64MHz            |                      |  |  |  |

| onment                     | 2.32 V~3.6 V/-40~85°C                                                          | 1.8 V~3.6 V/-40~85°C                                                                            | 1.8 V~3.6 V/-40~105°C | 1.8 V~3.6 V/-40~85°C |  |  |  |

| Universal                  |                                                                                | 1 pc (TIM3)                                                                                     |                       |                      |  |  |  |

| Advanced                   | <b>&gt;</b>                                                                    | 1 pc (TIM1)                                                                                     |                       |                      |  |  |  |

| Basic                      | 1 pc (TIM6)                                                                    |                                                                                                 |                       |                      |  |  |  |

| RTC                        | 1 pc (RTC)                                                                     |                                                                                                 |                       |                      |  |  |  |

| SPI                        | 2 pcs (SPI1, SPI2)                                                             |                                                                                                 |                       |                      |  |  |  |

| 12S                        | 2 pcs (I2S1, I2S2)                                                             |                                                                                                 |                       |                      |  |  |  |

| 12C                        | 1 pc (I2C)                                                                     |                                                                                                 |                       |                      |  |  |  |

| USART                      | 2 pcs (USART1, USART2)                                                         |                                                                                                 |                       |                      |  |  |  |

| LPUART                     | 1 pc (LPUART)                                                                  |                                                                                                 |                       |                      |  |  |  |

|                            | 21                                                                             |                                                                                                 |                       |                      |  |  |  |

|                            | 1(5)                                                                           |                                                                                                 |                       |                      |  |  |  |

| 10-bit ADC (channels) 1(8) |                                                                                |                                                                                                 |                       |                      |  |  |  |

|                            | (KB) (KB)  onment  Jniversal  Advanced  Basic  RTC  SPI  2S  2C  JSART  LPUART | ol (KB) (KB)  onment 2.32 V~3.6 V/-40~85°C  Universal Advanced Basic RTC SPI 2S 2C USART LPUART | SE   ST   SE   ST     | BLE5.1               |  |  |  |

| KEYSCAN       | 8/10/13 GPIOs support 44/65/104 keys respectively |

|---------------|---------------------------------------------------|

| IRC           | 1 pc                                              |

| CRC           | CRC16/CRC32                                       |

| Encapsulation | QFN32 (4 mm × 4 mm)                               |

### 2 Production Features

#### **2.1** Processor Core

N32WB03x series are integrated with ARM Cortex®-M0 processors.

# 2.2 Memory

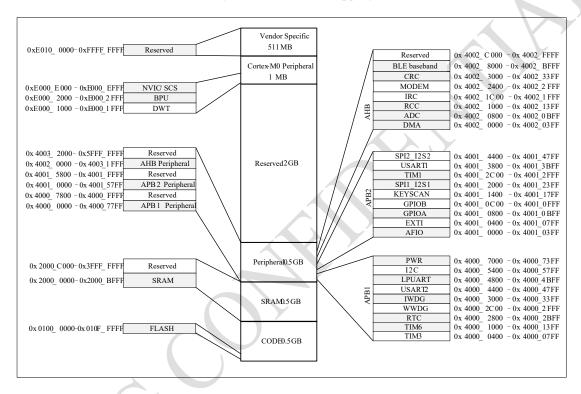

Figure 2-1 Memory Mapping

#### **2.2.1** Flash

256/512 KB Flash, with up to 256 KB for program storage and the remaining space for data storage.

#### **2.2.2 SRAM**

64KB SRAM, of which 16KB are dedicated to the BLE base band, and the remaining 48KB is used for BLE stack and user application.

#### **2.3** Low Power Modes

N32WB03x series support four low power modes.

Idle Mode

Only the CPU stops running. All peripherals are working and can wake up the CPU in the event of any interrupt/event.

Sleep Mode

The high speed clock is switched off. The power supply runs in the low power mode. The CORE power domain and BLE are turned off.

PD Mode

All systems are shut down. Only WAKEUP IO and NRST can be woken up.

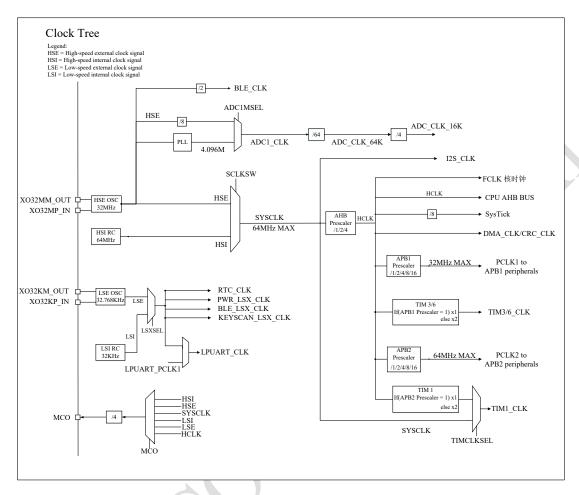

# **2.4** Clock System

Two high speed clocks:

- HSI oscillator clock (64 MHz)

- HSE oscillator clock (32 MHz)

Two secondary clock sources:

- LSI oscillator clock (32 KHz)

- LSE oscillator clock (32.768 KHz)

After the system is powered on and reset, HSI and HSE are enabled and the system clock is set to HSI by default. LSI can be used to drive the IWDG. Both LSI and LSE can selectively drive RTC, KEYSCAN and LPUART through a program. Moreover, LSI/LSE can automatically wake up the system in the Idle /Sleep/PD mode. If not in use, either clock source can be turned on or off independently to optimize system power dissipation.

Figure 2-2 Clock Tree

#### General Purpose Input/Output (GPIO) 2.5

GPIO stands for general purpose input/output. AFIO stands for alternate-function input/output. A chip supports up to 21 GPIOs, which are divided into 2 groups (GPIOA/GPIOB). GPIOA has 7 ports and GPIOB has 14 ports. GPIO ports share pins with other multiplexed peripherals and can be flexibly configured as required. Each GPIO pin can be independently configured as an output, input, or multiplexed peripheral functional port, and configured with heavy current through capability.

#### Main features:

- GPIO ports can be configured through software to the following modes:

- Input floating

- Input pull-up

- Input pull-down

- Analog function

- Output open-drain

Email: sales@nsing.com.sg

- ♦ Output push-pull

- ◆ Alternate function push-pull

- ◆ Alternate function open-drain

- Separate bit setting or bit clearing function

- All I/O supports external interrupt

- All I/Os can be woken up from low power modes, with configurable rising or falling edge

- > Eight EXTIs can wake up the Sleep mode and all I/O can be multiplexed as EXTI

- > PB3 can wake up I/O from the PD mode

- > Support remapping of AFIO through software

- > Support GPIO locking mechanism and removal of locking status through resetting

- Each I/O port register bit is freely programmable, but it must be accessed as 32-bit words (16-bit half-word or 8-bit byte access is not allowed).

#### **2.6** EXTI

The EXTI consists of 14 edge detectors for generating interrupt/event requests. Each interrupt line can be independently configured as an event or interrupt and the corresponding trigger event (rising edge or falling edge or both). Each line can also be masked independently. A pending register maintains the status line of the interrupt request. This request can be cleared by writing a '1' in the corresponding bit of the pending register.

#### **2.7 DMA**

DMA is integrated with one universal 5-channel DMA controller to manage data transfer from memory to memory, from peripheral to memory and from memory to peripheral;

Each channel has a dedicated hardware DMA request logic, and can be triggered by software. The transmission length, source address and destination address of each channel can be set separately by software.

DMA is applicable to main peripherals including SPI, I2S, I2C, USART, ADC, and basic, universal and advanced control TIMx.

### 2.8 CRC

CRC is integrated with CRC32 and CRC16 to get any CRC calculation based on a fixed polynomial. Among numerous applications, CRC-based technologies are used to verify the consistency of data transmission or storage. Within the scope specified in EN/IEC 60335-1, CRC provides a means of detecting flash memory errors, and can be used to compute software signatures in real time and compare them with the signatures generated when linking and generating the software.

Main features:

> CRC16: supports the polynomial X16+X15+X2+X0

- CRC16 computing time: one AHB clock period (HCLK)

- $\triangleright$  CRC32: supports the polynomial  $X_{32} + X_{26} + X_{23} + X_{22} + X_{16} + X_{12} + X_{11} + X_{10} + X_8 + X_7 + X_5 + X_4 + X_2 + X_{11} + X_{12} + X_{13} + X_{14} + X_{15} +$

- > CRC32 computing time: four AHB clock periods (HCLK)

- Configurable initial value of cyclic redundancy computation

- DMA available

# 2.9 Timer and Watchdog

$1 \times$  advanced timer,  $1 \times$  general-purpose timer,  $1 \times$  basic timer,  $2 \times$  watchdog timer, and  $1 \times$  system tick timer.

### 2.9.1 Basic Timer (TIM6)

TIM6 contains a 16-bit auto-loading counter driven by a programmable prescaler. It provides a time baseline for general-purpose timers.

#### Main features:

- ➤ 16-bit automatic reloading accumulating counter

- ➤ 16-bit programmable (can be modified in real time) prescaler, used for frequency demultiplication of the input clock by a coefficient ranging from 1 to 65536

- ➤ Generate an interrupt/DMA request when an event is updated (counter overflow)

# 2.9.2 General-purpose Timer (TIM3)

A general-purpose timer consists of one 16-bit countup/countdown auto-loading counter, one 16-bit prescaler, and 4 independent channels, each for input capture (pulse width measurement), output compare, PWM, and monopulse output;

- ➤ 16-bit countup, countdown, or countup/countdown auto-loading counter

- ➤ 16-bit programmable (can be modified in real time) prescaler; the frequency demultiplication coefficient of counter's clock frequency can be any numerical value ranging from 1 to 65536

- Four independent channels:

- ♦ Input capture

- Output compare

- PWM generation (edge or middle alignment)

- Monopulse output

- A synchronous circuit that uses an external signal control timer and allows interconnection of multiple timers

- > Generate interrupt/DMA in the case of the following events:

- ◆ Update: up/down counter overflow, counter initialization (software-based trigger or internal trigger)

- ◆ Trigger events (startup, shutdown, and initialization of counter, or internally triggered counting)

- ♦ Input capture

- Output compare

- > Support the incremental (quadrature) encoders for positioning and Hall sensor circuits

- Use trigger input signal as the input of external clock, or perform periodic current management

### 2.9.3 Advanced Timer (TIM1)

TIM1 consists of a 16-bit auto-loading counter driven by a programmable prescaler. It provides multiple functions, including measuring the pulse width of the input signal (input capture) or generating output waveform (such as output compare, PWM, and complementary PWM outputs with dead time in between). Using the timer's prescaler and RCC clock control prescaler can adjust the pulse width and waveform period from several microseconds to several milliseconds.

- ➤ 16-bit countup, countdown, or countup/countdown auto-loading counter

- ➤ 16-bit programmable (can be modified in real time) prescaler; the frequency demultiplication coefficient of counter's clock frequency can be any numerical value ranging from 1 to 65536

- > Use up to 64 MHz as timer's input clock

- Up to four independent channels:

- ♦ Input capture

- Output compare

- ◆ PWM generation (edge or middle alignment)

- ◆ Monopulse output

- > Trigger time points can be configured by software in the entire PWM cycle

- Complementary output with programmable dead time

- A synchronous circuit that uses an external signal control timer or allows interconnection of multiple timers

- A repetitive counter to update the timer registers only after a given number of cycles of the counter

- > Break input signal can put the timer's output signals in a reset state or in a known state

- ➤ Generate interrupt/DMA in the case of the following events:

- Update: up/down counter overflow, counter initialization (software-based trigger or internal/external trigger);

- ◆ Trigger events (startup, shutdown, and initialization of counter, or internally/externally triggered counting);

- ♦ Input capture;

- Output compare;

- Break signal input;

- Support the incremental (quadrature) encoders for positioning and Hall sensor circuits;

- > Use trigger input signal as the input of external clock, or perform periodic current management

In the debug mode, a counter can be frozen and PWM outputs are disabled, cutting off the switches controlled by those outputs. The advanced timer has many functions similar to and the same internal structure as that of the standard TIM timer. Therefore, it can work with the TIM timer through the timer's link function to provide synchronization or event link function.

### 2.9.4 System Tick Timer (Systick)

This timer is tailored to a real-time operating system and can also be used as a standard downcounter. It has the following features:

- ≥ 24-bit downcounter

- Automatic re-loading function

- > Generate a maskable system interrupt when the counter reaches zero

- Programmable clock source

### 2.9.5 Watchdog Timer (WDG)

It supports both independent watchdog (IWDG) and window watchdog (WWDG). Two watchdogs ensure higher security, time accuracy, and flexibility in use.

#### **Independent Watchdog (IWDG)**

The IWDG is based on a 12-bit downcounter and an 8-bit prescaler, and is driven by a separate, low speed RC oscillator. It still can work even if the master clock fails and operate in the Sleep mode. Once activated, the IWDG will generate a reset signal when the counter reaches 0x000 if the watchdog's counter is not cleared within a given time period. Moreover, it can also be used to reset the entire system in the event of an application error, or as a free timer to provide timeout management for applications.

#### Window Watchdog (WWDG)

The WWDG is typically used to monitor software failures caused by deviation of an application from the normal running sequence due to external disturbances or unforeseen logical conditions. Unless the value of a downcounter is refreshed before the T6 bit reaches zero, the watchdog circuit will generate a chip reset when the preset time cycle is reached. A chip reset is also generated if the value of a 7-bit downcounter (in the control register) is refreshed before the downcounter reaches the value of the window register. This indicates that the downcounter needs to be refreshed in a finite time window.

- > WWDG is driven by the clock obtained after frequency demultiplication of APB1 clock

- > Programmable free-running downcounter

- Conditional reset

- A reset occurs when the value of the downcounter is less than 0x40 if the watchdog is enabled;

- > A reset occurs when the downcounter is reloaded outside the window if the watchdog is enabled;

➤ If the watchdog is enabled and interrupt is allowed, an EWI is generated when the value of the downcounter reaches 0x40, and it can be used to reload the counter to avoid resetting WWDG.

#### **2.10** ADC

Support 10-bit 1.33 Msps ADC, single-ended or differential AMIC, and built-in PGA with a gain up to 42 dB.

Provide adjustable (1.6–2.3 V) MIC BIAS voltage for MIC.

Up to 8 channels, including 5 external single-ended channels, 1 differential MIC channel, and 2 internal channels. Two internal channels are VCC detection channel and temperature sensor channel. For 5 external channels, the detection range of channels 1 (PB10) and 2 (PB9) is 0V-1V, and that of channels 3 (PB8), 4 (PB7), and 5 (PB6) is 0V-3.6V. the input voltage of channels 3 (PB8), 4 (PB7), and 5 (PB6) <=VCC+300 mV.

In the audio mode, using the built-in PGA and microphone bias, MIC signals are amplified by the PGA, and then converted to digital signals by an ADC. After the audio input control (low-pass decimation filter and optional energy and zero-cross detection), the audio data is stored in the system RAM through DMA. Finally, 16-bit 16 kHz audio signal format data is output.

#### Main features:

- > Support AMIC input, with adjustable microphone bias

- > PGA supports single-ended or differential input and adjustable gain

- Support one ADC, which can measure 5 external single-ended channels, 1 differential MIC channel, and 2 internal channels (input channels are optional)

- Support two internal channels, including TempSensor and VCC

- > 10-bit 1.33 Msps ADC

- > Support digital decimation filter to 16-bit and noise filter

- Support single and continuous conversion modes

- A DMA request can be generated during channel switching

- ➤ The analog watchdog feature allows an application to detect whether the input PB10 voltage exceeds a user-defined high/low threshold

- > An interrupt occurs at the end of switching or in the case of an analog watchdog event

- > In the audio mode, the filter's output data is stored in a 16-bit data register, and in the general mode, the data is right-aligned and stored in a 16-bit data register

- In the audio mode, data is output in 16-bit 16 Ksps signed mono PCM format, and in the general mode, data is output in 10-bit 1.33 Msps unsigned format

# 2.11 I2C Bus Interface (I2C)

The I2C bus interface provides multi-master function that controls all the I2C bus specific sequences, protocol, arbitration and timing. It supports multiple communication rate modes (up to 1 MHz), DMA operations, and SMBus

2.0. The I2C module suits multiple purposes, including CRC code generation and verification, SMBus (System Management Bus), and PMBus (Power Management Bus).

- > Multi-master function: The module can be either a master device or a slave device

- > Functions of I2C master device

- ♦ Generate a clock

- Generate start and stop signals

- > Functions of I2C slave device

- ◆ Programmable address detection

- ◆ The I2C interface supports 7-bit or 10-bit addressing, and dual-slave address responsiveness in 7-bit slave mode

- ♦ Stop bit detection

- ➤ Generation and detection of 7-bit/10-bit addresses; broadcast call

- > Support different communication rates

- ◆ Standard rate (up to 100 kHz)

- ◆ Rapid (up to 400 kHz)

- ◆ Rapid+(up to 1 MHz)

- Support multiple status flags

- ◆ Transmitter/receiver mode flag

- ◆ End of byte transmission flag

- ♦ I2C bus busy flag

- Support multiple error flags

- ◆ Arbitration is lost in the master mode

- ◆ Acknowledgement (ACK) error after address/data transmission

- ◆ Detection of a start or stop condition of misplacement

- Overflow or underflow when the clock stretching function is disabled

- One interrupt vector:

- Event interrupt and error interrupt share an interrupt vector

- Optional clock stretching function

- DMA with single-byte cache

- Generation or verification of configurable PEC

- ◆ The PEC value can be transmitted as the last byte in the transmitter mode

- ◆ PEC for the last received byte

- Compatible with SMBus 2.0

- ◆ 25 ms clock low timeout delay

- ◆ 10 ms cumulative time for low clock extension for master device

- ◆ 25 ms cumulative time for low clock extension for slave device

- ◆ Generation or verification of hardware PEC with ACK control

- ◆ Support address resolution protocol (ARP)

- Compatible with SMBus

# **2.12** Universal Synchronous/Asynchronous Receiver/Transmitter (USART)

The USART is integrated with 3 serial receiver/transmitter interfaces, including USART1, USART2, and LPUART. USART1 and USART2 interfaces support synchronous/asynchronous communication, IrDA SIR ENDEC transmission coding and decoding, multiprocessor communication mode, single-wire half-duplex communication mode, and LIN master/slave function.

USART1 and USART2 interfaces also support the CTS and RTS hardware flow control, and the single-wire mode such as the ISO7816 smart card standard. DMA is available to both interfaces.

- > Full-duplex asynchronous communication

- ➤ Single-wire half-duplex communication

- NRZ standard format

- Fractional baud rate generator system a common programmable transmitting and receiving baud rate up to 4 Mbits/s

- Programmable data word length (8 or 9 bits)

- ➤ Configurable stop bits support for 1 or 2 stop bits

- LIN master is capable of sending synchronous break and LIN slave is capable of detecting the break: 13-bit break is generated and 10/11-bit break is detected when USART hardware is configured to LIN

- Transmitter clock output for synchronous transmission

- > IRDA SIR encoder-decoder: Support for 3/16 bit duration in normal mode

- > Smart card emulation capability

- ◆ The smart card interface supports the asynchronous smart card protocol as defined in the ISO7816-3 standard

- ◆ 0.5 and 1.5 stop bits for smart card

- ➤ Single-wire half-duplex communication

- Configurable multi-buffer communication using DMA buffering of received/transmitted bytes in SRAM using centralized DMA

- > Separate enable bits for transmitter and receiver

- Detection flags

- ◆ Receive buffer full

- ◆ Transmit buffer empty

- ◆ End of transmission flags

- Checking control

- ♦ Send check bits

- ♦ Check the received data

- Four error detection flags

- ♦ Overflow error

- ♦ Noise error

- ♦ Frame error

- Checking error

- Ten USART interrupt sources with flags

- ◆ CTS change

- ♦ LIN break detection

- ◆ Transmit data register empty

- ◆ Transmission completed

- ◆ Receive data register full

- ♦ Detected idle bus

- Overflow error

- Frame error

- ♦ Noise error

- ◆ Checking error

- Multiprocessor communication If addresses do not match, enable the silent mode

- Wake up from silent mode (by detecting idle bus or address flag)

- Two ways to wake up the receiver: address bit (MSB, 9th bit), bus idle

- ➤ Mode configuration:

| Communication mode               | USART1    | USART2    | LPUART        |

|----------------------------------|-----------|-----------|---------------|

| Asynchronous mode                | Supported | Supported | Supported     |

| Hardware flow control            | Supported | Supported | Supported     |

| Multi-buffer communication (DMA) | Supported | Supported | Supported     |

| Multiprocessor communication     | Supported | Supported | Not supported |

| Synchronous                      | Supported | Supported | Not supported |

| Single-wire half-duplex          | Supported | Supported | Not supported |

| Smart card                       | Supported | Supported | Not supported |

| IrDA                             | Supported | Supported | Not supported |

| LIN                              | Supported | Supported | Not supported |

# 2.13 Serial Peripheral Interface (SPI)

Two SPIs are provided, allowing half-duplex/full-duplex, synchronous, and serial communication between chips and peripherals. SPI can be configured to operate in the master mode and provide a communication clock (SCK) for the external slave device. Moreover, SPI can also work in the multi-master mode and use the CRC based reliable communication.

- Full-duplex synchronous transmission

- > Double-wire simplex synchronous transmission with/without the third two-way data cable

- > 8-bit or 16-bit transmission frame format

- > Support master or slave mode

- Support multi-master mode

- Rapid communication between master and slave modes

- NSS management can be performed by software or hardware in the master or slave mode: dynamic switching of master/slave mode

- Programmable clock polarity and phase

- Programmable data sequence, with MSB or LSB in the first order

- Dedicated transmit and receive flags to trigger interrupt

- > SPI bus busy flag

- Support reliable communication based on hardware CRC

- ◆ The CRC value can be transmitted as the last byte in the transmitter mode

- ◆ Automatic CRC for the last received byte in the full-duplex mode

- Master mode failure, overload, and CRC error flags that trigger interrupt

- Single-byte transmitting and receiving buffers with DMA feature: Generate transmission and receiving requests

- Maximum interface rate: 16 Mbps

### 2.14 Serial Audio Port (I2S)

I2S, a 3-pin synchronous serial interface communication protocol, operates in master or slave mode, supports an audio sample frequencies ranging from 8 kHz to 96 kHz, and can be configured as 16/24/32-bit transmission or as input or output channel. It is compatible with four audio standards, namely, the Philips' I2S standard, the MSB and LSB alignment standards, and the PCM standard.

It works in both master and slave modes in half-duplex communication. When it works as the master device, it provides clock signals to external slave devices through the interface.

- ➤ Half-duplex communication (either transmitting or receiving only at a time)

- Master or slave operation

- ➤ 8-bit linear programmable prescaler, helping obtain an accurate audio sample frequency (8 kHz~96 kHz)

- ► 16/24/32-bit data format

- ➤ 16-bit (16-bit data frame) or 32-bit (16/24/32-bit data frame) fixed packet frame for audio channel

- Programmable clock polarity (stable state)

- > Underflow flag bit in the slave transmitter mode and overflow flag bit in the master/slave receiving mode

- ➤ 16-bit data register to transmit and receive, one in each end of the channel

- Supported I2S protocols

- Philips' I2S standard

- ◆ MSB alignment standard (left-justified)

- ◆ LSB alignment standard (right-justified)

- ◆ PCM standard (a 16-bit channel frame with long or short frame synchronization; or extension from a 16-bit data frame to a 32-bit channel frame)

- Data sequence: MSB is always in the first order

> DMA is available to both transmitter and receiver

### 2.15 Real Time Clock (RTC)

RTC has a set of BCD timers/counters that count independently continuously. In the corresponding software configuration, RTC can provide the calendar function. RTC also has a programmable alarm clock interrupt.

The two 32-bit registers contain the subsecond, second, minute, hour (in 12- or 24-hour format), day of the week, day (day of the month), month, and year data in decimal format (BCD).

The subsecond value is provided by a separate 32-bit register in binary format. The other 32-bit register contains programmable second, minute, hour, day of the week, day, month, and year data.

RTC has the feature of automatic wakeup in the low power mode.

# 2.16 Infrared Controller (IRC)

The infrared controller can generate different infrared protocol signals by configuring different types of coding through software, and supports the software-based infrared self-learning function.

#### Main features:

- Carrier frequency range: 30 kHz~60 kHz

- Support pulse width coding and pulse spacing coding

- > Support Manchester coding

- Support carrier-free mode

- > Support any combination of Mark code and Space code

- ➤ Provide 16 (depth) × 21-bit (width) Code FIFO for storing coded commands

- Support repeatedly sending commands

- Generate interrupt upon the end of transmission

# 2.17 Automatic Key Scanning (KEYSCAN)

Support 8/10/13 IO ports that support 44/65/104 keys respectively.

Support configurable key jitter elimination.

Support automatic scanning, software scanning, low-power dissipation scanning modes.

- Automatic mode: Scanning performs at the configured fixed time interval

- Low power mode: A round of scanning (three times) is performed after the detection key is pressed

- Software mode: Scanning is triggered by the software

# **2.18** Serial SWD Debugging Interface (SWD)

A SWJ-DP interface with built-in ARM, it integrates JTAG and serial single-wire debugging interfaces, and supports connecting to the serial single-wire debugging interface or JTAG interface. The TMS and TCK signals of JTAG share pins with SWDIO and SWCLK respectively.

# 3 Definition and Description

# 3.1 Encapsulation Diagram

# 3.1.1 QFN32

Figure 3-1 QFN32 Pin Distribution of N32WB03x Series

# 3.2 Definition of Pin Multiplexing

Table 3-1 Definition of Pin

| Pin No.<br>(QFN32) | Pin Name<br>(Default Function) | Туре | Alternate Function                                              | Function Description      |

|--------------------|--------------------------------|------|-----------------------------------------------------------------|---------------------------|

| 1                  | PA2                            | I/O  | SPI1_MOSI(I2S1_SD)<br>KEY3                                      | 4                         |

| 2                  | PA3                            | I/O  | SPI1_MISO<br>KEY4                                               |                           |

| 3                  | RESET                          | AIO  |                                                                 |                           |

| 4                  | PB0                            | I/O  | TIM1_CH1 SPI2_NSS(I2S2_WS) USART1_RTS LPUART_RTS KEY11          |                           |

| 5                  | PA4<br>(SWDCLK)                | I/O  | TIM1_CH3N<br>USART1_TXD(7816_TX1)<br>KEY9                       |                           |

| 6                  | PA5<br>(SWDIO)                 | I/O  | TIM1_ETR<br>USART1_RXD(7816_RST1)<br>KEY10                      |                           |

| 7                  | PA6                            | I/O  | TIM1_BKIN USART2_TXD USART1_CK(7816_CLK1) KEY5                  |                           |

| 8                  | VDD_FLASH                      | S    |                                                                 | External 2.2 uF capacitor |

| 9                  | PB8<br>(XO32KP_IN)             | I/O  | TIM1_CH1<br>IIC_SDA<br>USART1_RTS<br>KEY7                       | ADC3                      |

| 10                 | PB9<br>(XO32KM_OUT)            | I/O  | TIM1_CH2 IIC_SCL USART1_CTS KEY8                                | ADC2                      |

| 11                 | PB1                            | I/O  | TIM1_CH2 SPI2_CLK(I2S2_CLK) USART1_CTS LPUART_TXD KEY12 ANT_SW4 |                           |

|    |         |     | TIM1_CH3              |           |

|----|---------|-----|-----------------------|-----------|

| 12 |         |     | SPI2_MOSI             |           |

|    | PB2     | I/O | LPUART_RXD            |           |

|    |         |     | KEY13                 |           |

|    |         |     | ANT_SW5               |           |

|    |         |     | TIM1_CH4              |           |

|    |         |     | SPI2_MISO             |           |

| 13 | PB3     | I/O | LPUART_CTS            | WAKEUP    |

|    |         |     | PA_LDO_EN             |           |

|    |         |     | ANT_SW1               |           |

|    |         |     | SPI2_CLK(I2S2_CLK)    |           |

|    |         |     | TIM3_CH1(IRC_TX)      |           |

| 14 | PB4     | I/O | USART2_TXD(7816_TX2)  |           |

|    |         |     | ANT_SW6               |           |

|    |         |     | SPI2 MISO             |           |

|    |         |     | TIM3 CH2(IRC RX)      |           |

| 15 | PB5     | I/O | USART2_RXD(7816_RST2) |           |

|    |         |     | RCC_MCO               |           |

|    |         |     | ANT_SW7               |           |

|    |         |     | SPI2_MOSI(I2S2_SD)    |           |

|    | PB6     | 1/0 | TIM3_CH3              |           |

|    |         |     | IIC_SDA               | ADC5      |

| 16 |         |     | USART1_TXD            |           |

|    |         |     | SWDCLK                |           |

|    |         |     | ANT_SW2               |           |

|    |         |     | SPI2_NSS(I2S2_WS)     |           |

|    |         |     | TIM3_CH4              |           |

|    | PB7     |     | IIC_SCL               |           |

| 17 |         | I/O | USART1_RXD            | ADC4      |

|    |         |     | SWDIO                 |           |

|    |         |     | ANT_SW3               |           |

|    |         |     | TIM1_CH3              |           |

|    |         |     | LPUART_RTS            |           |

| 18 | PB10    | I/O | USART2_RXD            | ADC1      |

|    |         |     | IIC_SMBA              |           |

|    |         |     | KEY6                  |           |

| Y  | 19 PB12 |     | TIM1_CH1N             |           |

| 19 |         | I/O | LPUART_TXD            | AMIC_BIAS |

|    |         |     | USART2_CTS            | _         |

|    |         |     | TIM1_CH4              |           |

| 20 | PB11    | I/O | _<br>LPUART_RXD       | AMIC_N    |

|    |         |     | USART2_RTS            |           |

|    |         |     | _                     |           |

|    | 1          |     |                    |                  |       |  |

|----|------------|-----|--------------------|------------------|-------|--|

|    |            |     | TIM1_CH2N          |                  |       |  |

| 21 | PB13       | I/O | LPUART_CTS         | AMIC_P           |       |  |

|    |            |     | USART2_CK          |                  |       |  |

| 22 | VCC        | S   |                    | Power supply for |       |  |

| 22 | VCC        | 3   |                    | chip             |       |  |

| 22 | GWITGH     | G.  |                    | DCDC external    |       |  |

| 23 | SWITCH     | S   |                    | Interface        |       |  |

| 24 | VDCDC      | S   |                    | DCDC output      |       |  |

| 25 | RFIOP      | AIO |                    | Antenna port     |       |  |

| 26 | VDD_PA     | S   |                    | PA power supply  |       |  |

|    |            |     |                    | DCDC output,     |       |  |

| 27 | VDCDCRF    | S   |                    | connecting to    |       |  |

|    |            |     |                    |                  | VDCDC |  |

|    |            |     |                    | Power supply for |       |  |

| 28 | VCCRF      | S   |                    | chip             |       |  |

|    |            |     |                    | External 32 MHz  |       |  |

| 29 | XO32MM_OUT | AIO |                    | crystal          |       |  |

| 20 | VO22MD IN  | AIO |                    | External 32 MHz  |       |  |

| 30 | XO32MP_IN  | AIO |                    | crystal          |       |  |

| 21 | D. O       | 1/0 | SPI1_NSS(I2S1_WS)  |                  |       |  |

| 31 | PA0        | I/O | 1/0                | 1/0              | KEY1  |  |

| -  | 5          |     | SPI1_CLK(I2S1_CLK) |                  |       |  |

| 32 | PA1        | I/O | KEY 2              |                  |       |  |

| 33 | GND        | S   |                    | Ground           |       |  |

I = input, O = output, S = power supply, AIO = analog IO

Upon resetting, the I/O port is configured to the analog input mode. But the following signals are not applicable:

- ➤ Input pull-up mode for NRST by default

- ➤ PA4: SWCLK under the input pull-down mode

- > PA5: SWDIO under the input pull-up mode

#### 4 Electrical Characteristics

### **4.1** Test Condition

All voltages are based on V<sub>SS</sub> unless otherwise specified.

#### 4.1.1 Minimum and Maximum

Unless otherwise specified, all minimums and maximums will be guaranteed under the worst ambient temperature, supply voltage and clock frequency conditions by testing 100% of the product at ambient temperature  $T_A$ =25°C and  $T_A$ = $T_{Amax}$  ( $T_{Amax}$  matches the specified temperature range) on the production line.

The annotations listed below each table are the data obtained through laboratory tests, design simulations and/or process characteristics, and will not be tested on the production line. On the basis of laboratory tests, the minimums and maximums are obtained by taking the average of the samples tested and adding to or subtracting from it three times the standard deviation (average  $\pm 3\sum$ ).

### 4.1.2 Typical Values

Unless otherwise specified, the typical data is based on  $T_A$ =25°C and VCC=3.3 V (1.8V/2.32 V $\leq$ VCC $\leq$ 3.6 V). Such data is used for guiding the design only and is not tested.

### 4.1.3 Typical Curve

Unless otherwise specified, the typical curve is used for guiding the design only and is not tested.

# 4.1.4 Load Capacitance

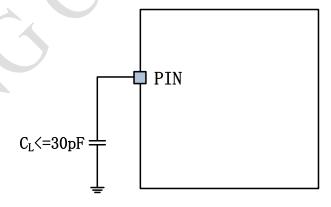

Figure 4-1 shows the load conditions for measuring pin parameters.

Figure 4-1 Load Conditions for Pins

# 4.1.5 Input Voltage of Pin

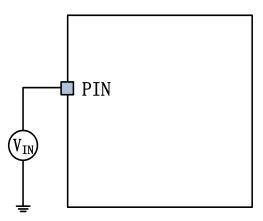

Figure 4-2 shows how to measure the input voltage of a pin.

Figure 4-2 Input Voltage of Pin

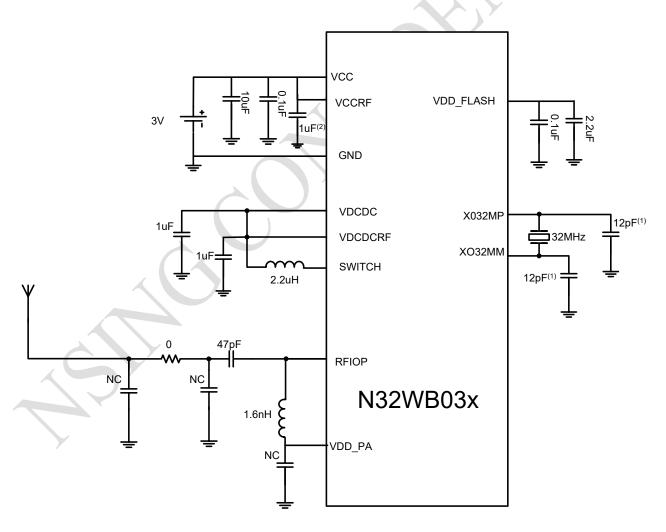

# 4.1.6 Power Supply Plan

Figure 4-3 Power Supply Plan

(a) VDCDC/VDCDCRF uses the internal DCDC power supply

- (b) VDCDC/VDCDCRF uses the external power supply

- (1) The load capacitance  $C_L$  required by different crystals or resonators is usually different, refer to section 4.3.6 for details.

- (2)In the case of low ripple requirements, the 1uF capacitor can be used without soldering.

# **4.1.7** Current Consumption Measurement

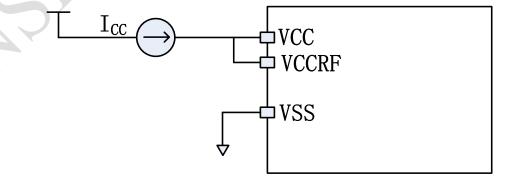

Figure 4-4 Current Consumption Measurement Plan

# 4.2 Absolute Maximum Rating

The load applied to the device in excess of the value given in the "absolute maximum rating" tables (Tables 4-1, 4-2, and 4-3) may cause permanent damage to the device. The maximum allowable load is given here, but it does not mean that the functions of the device work well under these conditions. The device reliability will be affected if the device works at the maximum conditions for a long time.

Table 4-1 Voltage Characteristics

| Symbol          | Description                                                           | Minimum            | Maximum | Unit |

|-----------------|-----------------------------------------------------------------------|--------------------|---------|------|

| VCC-VSS         | External main supply voltage (including VCCRF and VCC) <sup>(1)</sup> | -0.3               | 3.6     | V    |

| V <sub>IN</sub> | Input voltage on other pins <sup>(2)</sup>                            | VSS-0.3            | VCC+0.3 |      |

| Vesd(hbm)       | Electrostatic discharge (ESD) voltage (human body model)              | See Section 4.3.10 |         |      |

<sup>(1)</sup> All power supply (VCC, VCCRF) and ground (VSS) pins must be connected to an external power supply system within the permissible range.

Table 4-2 Current Characteristics

| Symbol                                       | Description                                                                         | Maximum (1) | Unit |

|----------------------------------------------|-------------------------------------------------------------------------------------|-------------|------|

| Ivcc                                         | Total current (supply current) passing through VCC/VCCRF power cable <sup>(1)</sup> | 150         |      |

| Ivss                                         | Total current (output current) passing through VSS ground wire <sup>(1)</sup>       | 150         |      |

| I <sub>IO</sub> I <sub>INJ(PIN)</sub> (2)(3) | Output sink current of any I/O and control pins                                     | 12          |      |

|                                              | Output current of any I/O and control pins                                          | -12         | A    |

|                                              | Injection current of NRST pin                                                       | +/-5        | mA   |

|                                              | Injection current of HSE's OSC_IN pin and LSE's OSC_IN pin                          | +/-5        |      |

|                                              | Injection current of other pins <sup>(4)</sup>                                      | +/-12       |      |

| $\sum I_{\text{INJ(PIN)}}^{(2)}$             | Total injection current of all I/O and control pins <sup>(4)</sup>                  | +/-150      |      |

<sup>(1)</sup> All power supply (VCC, VCCRF) and ground (VSS) pins must be connected to an external power supply system within the permissible range.

<sup>(2)</sup>  $I_{INJ(PIN)}$  must not exceed its limit (see Table 4-2), ensuring that  $V_{IN}$  does not exceed its maximum. If impossible, you need to guarantee that the external limit  $I_{INJ(PIN)}$  does not exceed its maximum. When  $V_{IN}$ <0.58, there is a reverse injection current.

<sup>(2)</sup> I<sub>INJ(PIN)</sub> must not exceed its limit, ensuring that V<sub>IN</sub> does not exceed its maximum. If impossible, you need to guarantee that the

external limit I<sub>INJ(PIN)</sub> does not exceed its maximum.

(3) When several I/O ports have injection current simultaneously, the maximum  $\sum I_{INJ(PIN)}$  is the sum of immediate absolute values of forward injection current and reverse injection current.

Table 4-3 Temperature Characteristics

| Symbol | Description                  | Value        | Unit |

|--------|------------------------------|--------------|------|

| Tstg   | Storage temperature range    | -40 to + 125 | °C   |

| TJ     | Maximum junction temperature | 105          | °C   |

# **4.3** Operating Conditions

# **4.3.1** General Operating Conditions

Table 4-4 General Operating Conditions

| Symbol             | Parameter                     | Condition | Minimum | Maximum | Unit |

|--------------------|-------------------------------|-----------|---------|---------|------|

| ${ m f}_{ m HCLK}$ | Internal AHB clock frequency  |           |         | 64      |      |

| f <sub>PCLK1</sub> | Internal APB1 clock frequency |           |         | 32      | MHz  |

| f <sub>PCLK2</sub> | Internal APB2 clock frequency |           |         | 64      |      |

| VCC                | Standard operating voltage    | ) ′       | 1.8(1)  | 3.6     | V    |

| VCCRF              | Analog operating voltage      |           | 1.8(1)  | 3.6     | V    |

| TA                 | Ambient temperature           |           | -40     | 85      | °C   |

| Тл                 | Junction temperature range    |           | -40     | 105     | °C   |

<sup>(1)</sup> When the voltage on VCC/VCCRF fluctuates, N32WB031KEQ6-2 ensure that the minimum voltage fluctuation is greater than 2.32 V.

# 4.3.2 Power-on and Power-off Operating Conditions

The parameters in the following table are obtained by testing at the ambient temperature listed in Table 4-4.

Table 4-5 Power-on and Power-off Operating Conditions

| Symbol | Parameter          | Condition | Minimum | Maximum | Unit |  |

|--------|--------------------|-----------|---------|---------|------|--|

| Tvcc   | VCC rising speed   | VCC-2.2.V | 20      | 8       | μs/V |  |

|        | VCC lowering speed | VCC=3.3 V | 100     | 8       |      |  |

#### 4.3.3 Characteristics of Built-in Reset and Power Control Module

The parameters given in the following table are obtained by testing at the ambient temperature and VCC supply voltage listed in Table 4-4.

Table 4-6 Characteristics of Built-in Reset and Power Control Module<sup>(1)</sup>

| Symbol           | Parameter                       | Condition            | Minimum | Typical Value       | Maximum | Unit |

|------------------|---------------------------------|----------------------|---------|---------------------|---------|------|

| V <sub>BOR</sub> | VCC threshold power-on voltage  | T <sub>A</sub> =25°C |         | 1.65 <sup>(2)</sup> |         | V    |

|                  | VCC threshold power-off voltage | T <sub>A</sub> =25°C |         | 1.60(2)             |         | V    |

| VBORhyst         | BOR delay                       | T <sub>A</sub> =25°C |         | 20                  |         | mV   |

<sup>(1)</sup> They are guaranteed by the design and are not tested in production.

#### **4.3.4** Characteristics of DCDC

DCDC is an internal voltage generation module. The parameters given in the following table are obtained by testing at the ambient temperature and VCC supply voltage listed in Table 4-4.

Table 4-7 Built-in DCDC Power Management Module Characteristics (1)

| Symbol            | Parameter                                 | Condition                    | Minimum | Typical<br>Value | Maximum | Unit |

|-------------------|-------------------------------------------|------------------------------|---------|------------------|---------|------|

| VCC               | Supply voltage                            |                              |         | 3.3              |         | V    |

| VDCDC             | DCDC output voltage                       |                              |         | 1.15             |         | V    |

| Iload             | DCDC current carrying capacity            | Output current@ VDCDC=1.15 V |         |                  | 20      | mA   |

| л                 | DCDC conversion efficiency <sup>(2)</sup> |                              |         | 82.5             |         | %    |

| $V_{RPL}$         | DCDC output voltage fluctuation           |                              |         | 10               |         | mV   |

| L                 | DCDC load inductance                      |                              | 1       | 2.2              | 10      | μН   |

| Соит              | DCDC load capacitance                     |                              | 0.5     | 2                | 10      | μF   |

| t <sub>STAR</sub> | DCDC output voltage setup time            |                              |         | 90               |         | uS   |

<sup>(2)</sup> N32WB031KEQ6-2 VCC threshold power on voltage 2.27V, VCC threshold power off voltage 2.25V.

- (1) They are guaranteed by the design and are not tested in production.

- (2) The FDK MIPSDZ1608G2R2PA inductor is used in test. Different inductor models may vary in DCDC efficiency.

### 4.3.5 Characteristics of Supply Current

Current consumption is a composite indicator evaluated based on multiple parameters and factors, including operating voltage, ambient temperature, I/O pin load, software configuration, operating frequency, I/O pin switching rate, position of a program in memory, and code executed.

For the detailed method to measure current consumption, see Figure 4-4.

#### 4.3.5.1 Typical Current Consumption

Table 4-8 Typical Current Consumption in Sleep Mode<sup>(1)</sup>

| Symbol | Parameter             | Condition                                                      | Minimum | Typical<br>Value <sup>(1)</sup> | Maximum <sup>(1)</sup> | Unit |

|--------|-----------------------|----------------------------------------------------------------|---------|---------------------------------|------------------------|------|

| Icc    | Current in Sleep mode | Low speed clock: ON; 48 KB SRAM retention; I/O state unchanged |         | 1.6                             | 3.8                    | uA   |

| 100    | Current in PD mode    | VCC is maintained; WAKEUP IO and NRST can be woken up          |         | 0.13                            | 1.0                    | uA   |

<sup>(1)</sup> The test condition is  $T_A=25$ °C, VCC=3.3 V.

#### 4.3.5.2 Typical Current Consumption in Operating Mode

The chip is under the following conditions:

- All I/O pins are reset.

- All peripherals are turned off unless otherwise specified.

- Ambient temperature and VCC supply voltage conditions are listed in Table 4-4.

Table 4-9 Typical Current Consumption in Operating Mode

| Symbol | Parameter                        | Condition                                              | Typical Value(1) | Maximum | Unit |

|--------|----------------------------------|--------------------------------------------------------|------------------|---------|------|

| Icc    | Supply current in operating mode | High speed internal RC oscillator (HSI) <sup>(2)</sup> | 2.0              |         | mA   |

- (1) The typical value is measured at T<sub>A</sub>=25°C and VCC=3.3 V.

- (2) High speed internal clock is 64 MHz.

Table 4-10 BLE Power Dissipation

| Symbol | Parameter | Condition | Typical Value <sup>(1)</sup> | Maximum | Unit |

|--------|-----------|-----------|------------------------------|---------|------|

|--------|-----------|-----------|------------------------------|---------|------|

|     |                                  | 0 dbm transmitting power, VCC current           | 4.2 |          | mA |

|-----|----------------------------------|-------------------------------------------------|-----|----------|----|

|     |                                  | Minimum RX sensitivity, VCC current             | 3.8 |          | mA |

| Icc | Supply current in operating mode | 1 s broadcast interval, VCC average current     | 13  | 4        | uA |

|     |                                  | 100 ms broadcast interval, VCC average current  | 109 | 1        | uA |

|     |                                  | 100 ms connection interval, VCC average current | 70  | <b>\</b> | uA |

<sup>(1)</sup> The typical value is measured at T<sub>A</sub>=25°C and VCC=3.3 V.

#### 4.3.6 Characteristics of External Clock Source

#### 4.3.6.1 High Speed External Clock Generated Using a Crystal/Ceramic Resonator

The high speed external clock (HSE) can be generated by an oscillator consisting of a 32 MHz crystal/ceramic resonator. The data presented in this section is obtained from the overall characteristic evaluation using the typical external components listed in the table below. In applications, the resonator and load capacitor must be as close to the pin of the oscillator as possible to reduce output distortion and stabilization time at startup. For more parameters (such as frequency, encapsulation, and precision) of a crystal resonator, please contact the manufacturer. (The crystal resonator mentioned here usually means the passive crystal oscillator.)

Table 4-11 Characteristics of HSE 32 MHz Oscillator<sup>(1)(2)</sup>

| Symbol                                         | Parameter                                                                                   | Condition              | Minimum | Typical<br>Value | Maximum | Unit |

|------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------|---------|------------------|---------|------|

| fosc_in                                        | Oscillator frequency                                                                        |                        |         | 32               |         | MHz  |

| C <sub>L1</sub> C <sub>L2</sub> <sup>(3)</sup> | Recommended load capacitance and corresponding crystal serial impedance (RS) <sup>(4)</sup> | $RS = 100\Omega^{(4)}$ |         | 12               |         | pF   |

| ID                                             | HSE drive current                                                                           | VCC=3.3 V, 12 pF load  |         | 0.2              |         | mA   |

| t <sub>SU(HSE)</sub> (5)                       | Startup time                                                                                |                        |         | 0.2              |         | ms   |

<sup>(1)</sup> Resonator's characteristic parameters are given by the manufacturers of crystal/ceramic resonators.

<sup>(2)</sup> They are obtained from laboratory tests and are not tested in production.

<sup>(3)(4)</sup> For C<sub>L1</sub> and C<sub>L2</sub>, it is recommended to use high-quality ceramic dielectric capacitors designed for high frequency applications and

select suitable crystals or resonators. C<sub>L1</sub> and C<sub>L2</sub> usually share same parameters. Crystal manufacturers usually give the parameter of load capacitance as a serial combination of CL1 and CL2. When selecting C<sub>L1</sub> and C<sub>L2</sub>, you should consider the capacitive reactance of PCB and chip pins.

(5) t<sub>SU(HSE)</sub> is the startup time, which is measured from the moment when the software enables HSE until a stable 32 MHz oscillation is obtained. This value is measured on a standard crystal resonator and may vary greatly depending on the crystal manufacturer.

Figure 4-5 Typical Application with a 32 MHz Crystal

(1) The value of REXT depends on the characteristics of the crystal.

#### 4.3.6.2 Low Speed External Clock Generated Using a Crystal/Ceramic Resonator

The low speed external clock (LSE) can be generated by an oscillator consisting of a 32.768 kHz crystal/ceramic resonator. The data presented in this section is obtained from the overall characteristic evaluation using the typical external components listed in the table below. In applications, the resonator and load capacitor must be as close to the pin of the oscillator as possible to reduce output distortion and stabilization time at startup. For more parameters (such as frequency, encapsulation, and precision) of a crystal resonator, please contact the manufacturer. (The crystal resonator mentioned here usually means the passive crystal oscillator.)

Notes: For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use ceramic dielectric capacitors between 8 pF and 20 pF and select suitable crystals or resonators.  $C_{L1}$  and  $C_{L2}$  usually share same parameters. Crystal manufacturers usually give the parameter of load capacitance as a serial combination of  $C_{L1}$  and  $C_{L2}$ . Different crystals or resonators usually require different load capacitance (CL). The selected  $C_{L1}$  and  $C_{L2}$  must match the crystal or resonator used.

The load capacitance CL is calculated by the formula:  $CL = C_{L1} \times C_{L2} / (C_{L1} + C_{L2}) + C_{stray}$ , where,  $C_{stray}$  is the capacitance of the pin and the capacitance associated with the PCB or PCB, typically between 2 pF and 7 pF.

| Symbol                                         | Parameter                                                     | Condition     | Minimum | Typical<br>Value | Maximum | Unit |

|------------------------------------------------|---------------------------------------------------------------|---------------|---------|------------------|---------|------|

| C <sub>L1</sub> C <sub>L2</sub> <sup>(2)</sup> | Recommended load capacitance and corresponding crystal serial | RS: 30KΩ~90KΩ |         | 10               |         | pF   |

Table 4-12 Characteristics of LSE Oscillator (f<sub>LSE</sub>=32.768kHz)<sup>(1)</sup>

|                                     | impedance (RS) <sup>(3)</sup> |                                                         |      |    |

|-------------------------------------|-------------------------------|---------------------------------------------------------|------|----|

| I2                                  | LSE drive current             | VCC=3.3 V, $C_{L1}$ = $C_{L2}$ =10 Pf, RS=30 K $\Omega$ | 0.2  | μΑ |

| t <sub>SU(LSE)</sub> <sup>(4)</sup> | Startup time                  |                                                         | 0.84 | S  |

- (1) They are obtained from laboratory tests and are not tested in production.

- (2) See the "Notes" at the top of this table.

- (3) Using a high quality oscillator with a small RS value can optimize the current consumption. For more details, please contact the crystal manufacturer.

- (4) t<sub>SU(LSE)</sub> is the startup time, which is measured from the moment when the software enables LSE until a stable 32.768 KHz oscillation is obtained. This value is measured on a standard crystal resonator and may vary greatly depending on the crystal manufacturer.

Resonator integrated with capacitor C<sub>L1</sub> XO32KP\_IN Gain control

Figure 4-6 Typical Application with a 32.768 kH Crystal

### **4.3.7** Characteristics of Internal Clock Source

The characteristic parameters given in the following table are obtained by testing at the ambient temperature and supply voltage listed in Table 4-4.

#### High Speed Internal (HSI) RC Oscillator

**Typical** Symbol Condition Minimum Maximum Unit Parameter Value  $f_{HSI}$ Frequency  $T_A = 25$ °C 63.36 64 64.64 MHz  $T_A = -40 \sim 105$ °C, temperature drift -3 3 % Temperature drift of HSI **ACC**<sub>HSI</sub> oscillator  $T_A = -10 \sim 85$ °C, temperature drift -2 2 %

Table 4-13 Characteristics of HSI Oscillator<sup>(1)(2)</sup>

Email: sales@nsing.com.sg

|                      |                                     | $T_A = 0 \sim 70$ °C, temperature drift | -1 |     | 1   | %  |

|----------------------|-------------------------------------|-----------------------------------------|----|-----|-----|----|

| t <sub>SU(HSI)</sub> | Startup time of HSI oscillator      |                                         |    |     | 0.3 | μs |

| I <sub>CC(HSI)</sub> | Power dissipation of HSI oscillator |                                         |    | 180 | 260 | μА |

<sup>(1)</sup> VCC = 3.3 V,  $T_A = -40 \sim 105 ^{\circ}\text{C}$ .

#### Low Speed Internal (LSI) RC Oscillator

Table 4-14 Characteristics of LSI Oscillator<sup>(1)</sup>

| Symbol          | Parameter                           | Condition                                 | Minimum  | Typical<br>Value | Maximum | Unit |

|-----------------|-------------------------------------|-------------------------------------------|----------|------------------|---------|------|

| f(2)            | Output frequency                    | Calibrated at 25°C                        | 31.9     | 32               | 32.2    | KHz  |

| $f_{LSI}^{(2)}$ |                                     | $T_A = -40 \sim 85$ °C, temperature drift | -1       |                  | 1       | %    |

| tsu(LSI) (3)    | Startup time of LSI oscillator      |                                           | <b>Y</b> |                  | 200     | μs   |

| Icc(LSI) (3)    | Power dissipation of LSI oscillator |                                           |          | 0.23             |         | μΑ   |

<sup>(1)</sup> VCC = 3.3 V,  $T_A = -40 \sim 85^{\circ}\text{C}$ .

## 4.3.8 Time Required to Wake Up from Low Power Modes

The wakeup time listed in Table 4-15 is measured during the wakeup phase of a 64 MHz HSI RC oscillator. The clock source used in wakeup depends on the current operating mode:

Sleep or PD mode: The clock source is a RC oscillator