## **User Guide**

## **ADC** user guide

## Introduction

The MCU features a built-in advanced 12-bit ADC with calibration function, used to improve ADC accuracy under changing environmental conditions. This document aims to help users correctly use the ADC, reduce errors, and improve the stability of ADC operation. The main contents include:

- Correct configuration of three ADC clocks

- ADC calibration

- ADC state transition

- MR Voltage configuration

- ADC interference and errors

- ADC small signal acquisition

- Differential calculation formula

This document is only applicable to NSING MCU products, currently supported product series is N32G430.

## **Contents**

| 1. Overview                          | 3  |

|--------------------------------------|----|

| 1.1 SAR ADC                          | 3  |

| 1.2 Basic Operating Principle        | 3  |

| 2. ADC Application Considerations    |    |

| 2.1 ADC Clock Configuration          | 6  |

| 2.2 ADC Calibration                  |    |

| 2.3 MR Voltage                       | 8  |

| 2.4 ADC State Switching              | 9  |

| 2.5 ADC Error                        | 10 |

| 2.6 Small Signal Measurement         | 14 |

| 2.7 Differential Calculation Formula | 14 |

| 3. Conclusion                        | 10 |

| 4. Version History                   | 17 |

| 5. Notice                            | 18 |

### 1. Overview

#### 1.1 SAR ADC

The serie's ADCs are all 12-bit successive approximation analog-to-digital converters, supporting various operating modes to meet the needs of most analog-to-digital conversion applications. The ADC has three clocks: the operation clock, the sampling clock, and the timing clock, to ensure the ADC sampling rate and accuracy.

The process of external input signal acquisition is as follows: first, the channel and chip pins are connected via MUX to charge the sampling capacitor inside the chip, then the MUX disconnects the channel connection after the sampling is completed, keeping the input signal on the sampling capacitor. Finally, the converter sequentially compares and calculates the code value and transfers it to the data register.

RAIN (1)

VAIN

Parasitic capacitance

Sample and hold ADC converter

RADC (1)

L2 bits converter

CADC (1)

L2 bits converter

CADC (1)

Figure 1-1 Typical ADC Connections

The parameters marked in the figure are as follows:

V<sub>AIN</sub>: input signal.

R<sub>AIN</sub>: external input impedance.

C-parasitic: parasitic capacitance on PCB and pads.

A<sub>INX</sub>: signal input port.

R<sub>ADC</sub>: sampling switch resistance.

C<sub>ADC</sub>: internal sampling and hold capacitor.

## 1.2 Basic Operating Principle

The basic operating principle of an ADC consists of three processes: sampling, holding, and quantization. Sampling is the process of converting a continuously changing analog signal in time into a discrete analog signal, holding is the process of storing the signal for the next sampling, and quantization is the process of converting the held analog signal into a digital signal.

If the internal sampling and conversion circuit of the ADC is simplified, it can be equivalent to three working stages:

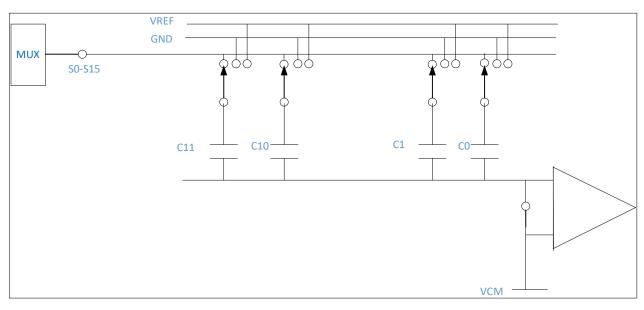

#### Sampling stage

S0~S15 are connected to chip pins (input signal sources) based on the configured channel selection. The sampling capacitors are C0 to C11, with the lower board of the capacitor connected to the signal source and the upper plate (COMP end) connected to VCM for input signal sampling.

Figure 1-2 Equivalent Circuit of Sampling Stage

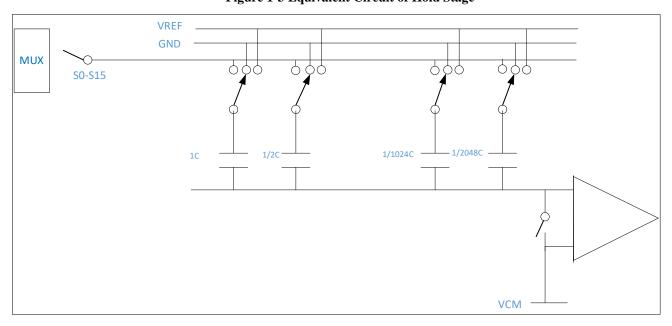

### Hold stage

Disconnect S0~S15 from the input signal, with the upper plate of the capacitor (COMP end) floating and the lower plate connected to ground.

Figure 1-3 Equivalent Circuit of Hold Stage

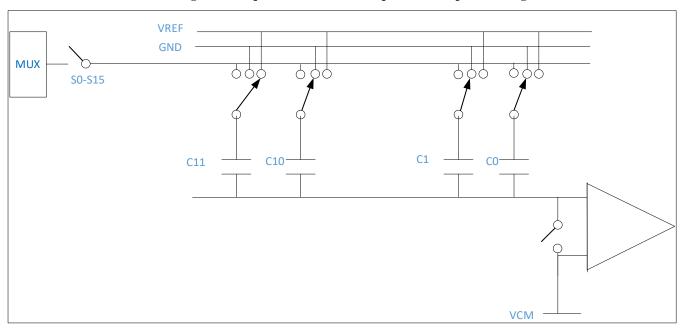

Sequential comparison stage

In the initial stage, the lower plate of the capacitor is connected from high to low to VREF, GND... GND, and from C11 to C0, the capacitor switch is decided based on the comparator output result:

- MSB: C11 is connected to VREF for comparison. If the comparator output is high, it remains connected to VREF; otherwise, it is changed to connect to GND.

- (M-1)SB: C10 is connected to VREF for comparison. If the comparator output is high, it remains in that state; otherwise, it is changed to connect to GND.

- Repeat the comparison process described above.

- LSB: C0 is connected to VREF for comparison. If the comparator output is high, it remains in that state; otherwise, it is changed to connect to GND.

- After the conversion is complete, move the quantized value to the data register.

Figure 1-4 Equivalent Circuit of Sequential Comparison Stage

## 2. ADC Application Considerations

In many applications, it is necessary to collect analog signals and perform calculations to achieve a series of functions. Therefore, the ADC is an important peripheral in the chip. High-precision ADC can ensure that the converted values of input signals are closer to the original signal source. However, errors become an unavoidable topic for ADCs. In order to reduce sampling signal errors, it is necessary not only to filter the noise in the input signal but also to correctly configure and use the ADC.

Below will be a detailed introduction to the application considerations of the ADC, aiming to reduce errors in data acquisition, obtain high-precision sampled data, and leverage the powerful performance of the ADC.

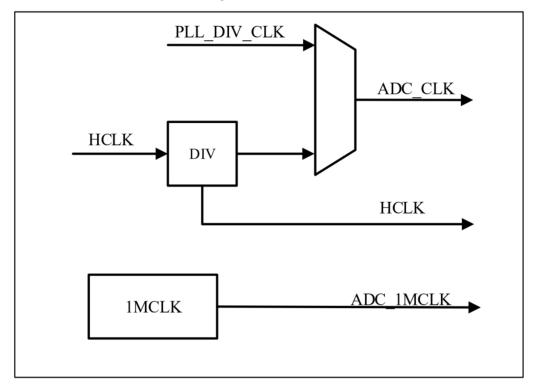

### 2.1 ADC Clock Configuration

Below will be a detailed introduction to the application considerations of the ADC, aiming to reduce errors in data acquisition, obtain high-precision sampled data, and leverage the powerful performance of the ADC.

Figure 2-1 ADC Clock

ADC operating clock

The operating clock used for accessing registers is HCLK;

Example of configuring the ADC operating clock in various series of library functions:

Figure 2-2 Clock Function

N32G430 series:

RCC\_AHB\_Peripheral\_Clock\_Enable(RCC\_AHB\_PERIPH\_ADC);

ADC sampling clock

The sampling clock ADC\_CLK has two sources (HCLK division or PLL division). The HCLK division is a synchronous clock with the system, while the PLL division is an asynchronous clock with the system. The advantage of using a synchronous clock is that there is no uncertainty when triggering the ADC response. The advantage of using the PLL division clock is that it can independently handle the ADC's operating clock without affecting other modules hanging on HCLK.

Example of configuring the ADC sampling clock in the N32G430 series library functions:

The N32G430 series has a maximum operating frequency of 128MHz and can configure the PLL as the sampling clock source, with a maximum frequency of 80MHz, supporting division factors of 1, 2, 4, 6, 8, 10, 12, 16, 32, 64, 128, 256. It can also configure AHB\_CLK as the sampling clock source, with a maximum frequency of 80MHz and supporting division factors of 1, 2, 4, 6, 8, 10, 12, 16, 32.

#### Figure 2-3 ADC Sampling Clock Function

When the system frequency is greater than 80MHz, the ADC\_CLK must be divided by at least 2.

AHB\_CLK as the sampling clock source: ADC\_Clock\_Mode\_Config(ADC\_CKMOD\_AHB,

RCC\_ADCHCLK\_DIV16);

PLL as the sampling clock source: ADC\_Clock\_Mode\_Config(ADC\_CKMOD\_PLL,

RCC\_ADCPLLCLK\_DIV2);

#### ADC timing clock

The timing clock can be HSI and HSE, mainly used for internal timing, and the frequency must be configured as 1MHz. Example of configuring the ADC timing clock in various series of library functions:

- For the N32G430 series, configuring the ADC timing clock, the clock source can be internal HSI and HSE. HSI is 8MHz, and HSE supports 4~32MHz.

#### **Figure 2-4 ADC Timing Clock Function**

HIS is 8MHZ:RCC\_ADC\_1M\_Clock\_Config(RCC\_ADC1MCLK\_SRC\_HSI, RCC\_ADC1MCLK\_DIV8);

HSE is 8MHZ:RCC\_ADC\_1M\_Clock\_Config(RCC\_ADC1MCLK\_SRC\_HSE, RCC\_ADC1MCLK\_DIV8);

#### 2.2 ADC Calibration

Calibration can increase sampling accuracy. Calibration is required when the ADC is powered up for the first time and when the ADC wakes up from deep sleep to ensure the sampling accuracy of the ADC.

The ADC digital calibration module is used to measure and correct the offset voltage of the ADC. The calibration process samples the ideal "0" voltage through internal connections, calculates the offset, and removes the offset voltage during normal operation.

**Figure 2-5 ADC Calibration Function**

N32G430 series, ADC calibration operation:

/\* Start ADC calibration \*/

ADC\_Calibration\_Operation(ADC\_CALIBRATION\_ENABLE);

/\* Check the end of ADC calibration \*/

while (ADC Calibration Operation(ADC CALIBRATION STS))

## 2.3 MR Voltage

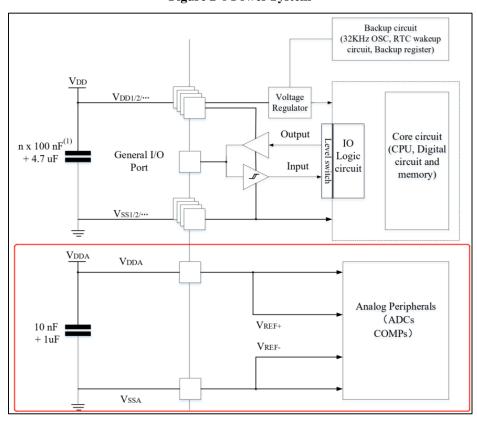

The chip power supply system consists of digital power supply and analog power supply. VDD mainly provides power to digital modules such as CPU, USART, GPIO, etc. VDDA mainly provides power to analog modules such as ADC, COMP, etc. It is recommended to use the same power supply for VDD and VDDA. During power-up and normal operation, a maximum difference of 300mV is allowed between VDD and VDDA.

Figure 2-6 Power System

The ADC module is powered by an internal LDO by default, with the LDO reference source initially set to VDDA. Fluctuations in the VDDA voltage can affect the ADC sampling accuracy and operation. In harsh working environments, there is a probability of abnormal ADC operation, manifested as abnormal or halted data acquisition. When using DMA for data transfer in multi-channel acquisition, there may also be a probability of channel shifting during data transfer.

When encountering similar phenomena in ADC applications, adjusting the MR voltage and switching the ADC power supply

to the digital system instead of using the internal LDO power supply method can effectively improve the stability of ADC operation.

MR voltage adjustment

#### Figure 2-7 MR Voltage Adjustment

- 1. Define the MR operation register: ADC\_LDO\_CTR (\*(uint32\_t\*)(0x40020800+0x60));

- 2. Before initializing the ADC registers, switch the ADC module to digital power supply:  $ADC\_LDO\_CTR \models 0x00000028;$

- 3. Normal initialization of ADC register parameters

### 2.4 ADC State Switching

In some application scenarios where the ADC working state needs to be switched multiple times, the ADC is repeatedly turned on and off. It is not enough to only operate the ON bit to enable or disable. It is also necessary to confirm the ADC status and determine whether the ADC state switch is completed before proceeding to the next step.

ADC power-up

When the ADC is powered up for the first time, it is necessary to wait for the Power Up process to complete. This can be confirmed by checking the RDY bit in ADC\_CTRL3 to see if the power-up is complete, and then proceed with the ADC calibration.

#### Figure 2-8 ADC Power-up

```

ADC power-up operation:

/* Enable ADC */

ADC_ON();

/* Check ADC Ready */

while(ADC_Flag_Status_Get(ADC_RD_FLAG, ADC_FLAG_JENDCA, ADC_FLAG_RDY) ==

RESET)

```

#### ADC power-down

By clearing the ON bit, conversions can be stopped, and the ADC can be placed in power-down mode, where the ADC consumes very little power (only a few uA). When powering down the ADC, users should check the PDRDY bit in ADC\_CTRL3 to confirm if the power-down is complete before proceeding to the next step.

When the ADC is disabled, it defaults to the power-down mode, where as long as it is not powered down, recalibration is not required as the calibration value is automatically retained by the ADC. To further reduce power consumption, the ADC has a deep sleep mode. When entering deep sleep mode after ADC DISABLE, the internal calibration value of the ADC is lost and recalibration is required.

Figure 2-9 ADC Power-down

```

ADC power-down operation:

/* Disable ADC ADC */

ADC_OFF();

/* Check ADC Power Down Ready */

while(ADC_Flag_Status_Get (ADC_RD_FLAG, ADC_FLAG_AWDG, ADC_FLAG_PD_RDY) ==

RESET);

```

#### Wake-up in low power mode

When the chip wakes up from low power mode, it is necessary to reset the ADC module clock and then perform the initialization configuration, otherwise it will affect the sampling accuracy of the ADC.

#### Figure 2-10 ADC Wake-up in Low Power Mode

After waking up in low power mode, re-initialize the ADC configuration, taking ADC1 as an example:

- 1. De-initialize ADC clock: ADC\_DeInit(ADC1);

- 2. ADC initialization configuration;

- 3. Enable ADC calibration

#### 2.5 ADC Error

In theory, the accuracy of an ADC is the smallest scale of the conversion code. However, in practical signal acquisition, various errors are superimposed. The actual accuracy of the ADC, after being affected by error interference, is  $V_{ref}/4096 + V_{error}$ .

The main factors affecting ADC errors are:

- Internal ADC errors, including offset error, gain error, differential nonlinearity error, integral nonlinearity error, etc.

- Reference voltage noise, in analog signal voltage acquisition, the reference voltage serves as the basis. Any noise on the reference voltage will cause the converted digital value to change.

- Analog input signal noise, electrical equipment can generate noise on the analog signal, causing fluctuations in the acquired values.

- I/O pin crosstalk, adjacent digital ports with high-frequency switching signals can introduce noise into the analog input signal of the ADC.

- Exceeding the chip specifications for analog signal voltage, if the analog I/O port input voltage is below -0.2V or above the VDD voltage, it will pull down or pull up the acquisition value.

- External signal impedance can affect sampling accuracy.

- Improper clock configuration, the ADC requires three clocks to be enabled, and any one of the clocks not configured correctly will affect the ADC accuracy.

To achieve the best sampling accuracy for the ADC, we can take the following measures:

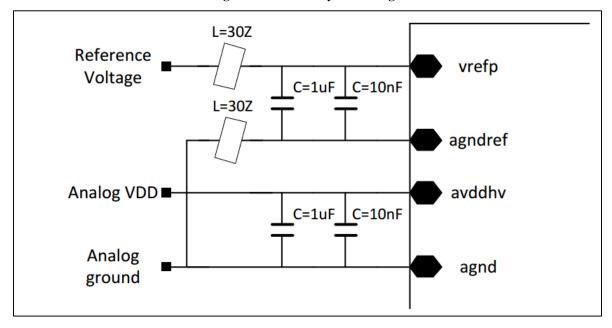

#### • Reduce power supply noise in PCB design

Power supply side: small capacitors filter high-frequency noise, while large capacitors filter low-frequency noise. It is recommended to place ceramic capacitors near the analog power (VDDA and VSSA) pins. These capacitors can filter noise introduced by PCB traces. Capacitors with small values can respond to rapid changes in current and quickly discharge to adapt to fast current changes.

Near the chip side: 10nF ceramic capacitor and 1uF tantalum capacitor/ceramic capacitor.

Figure 2-11 Power System Design

#### Process signal sources

- Average the sampled input signal values.

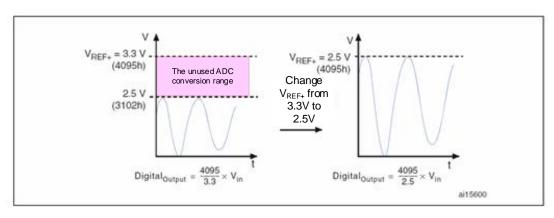

- Use a VREF that better matches the input range.

Figure 2-12 V<sub>ref</sub> Range

- Add an external filter to the input signal.

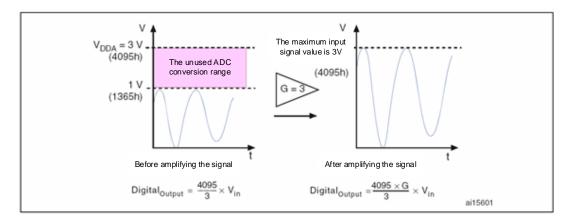

- Increase the signal amplitude to better match the ADC range.

Figure 2-13 ADC Value Range

• The input signal voltage meets the chip specifications

When using a certain ADC channel, negative voltage (such as -0.2V) should not be applied to other unused ADC sampling channels. Applying negative voltage to unused channels can lower the voltage of the normally sampled ADC channel, resulting in inaccurate data sampling. Similarly, when using a specific ADC channel, high voltage (greater than VDD voltage) should not be applied to other unused ADC sampling channels. Applying high voltage to unused channels can raise the voltage of the normally sampled ADC channel, leading to inaccurate data readings.

Choose an appropriate sampling period

During the sampling process of the ADC, it can be effectively equivalent to sampling the external signal source through capacitance. In actual circuits, the switches themselves have impedance, and the I/O channel routing also has impedance. The specific input impedance and the choice of sampling period can be indirectly obtained through Table 2-1.

**Table 2-1 ADC Sample Time**

| Input        | Resolution | Rin(kΩ) | Minimum<br>sample time<br>(ns) | Input        | Resolution | Rin(kΩ) | Minimum<br>sample time<br>(ns) |

|--------------|------------|---------|--------------------------------|--------------|------------|---------|--------------------------------|

| fast channel |            | 0       | 39.6                           |              |            | 0       | 79.2                           |

|              |            | 0.05    | 43.5                           |              | 12-bit     | 0.05    | 83.1                           |

|              |            | 0.1     | 47.4                           |              |            | 0.1     | 86.9                           |

|              | 10.11      | 0.2     | 55.1                           | slow channel |            | 0.2     | 94.7                           |

|              |            | 0.5     | 78.4                           |              |            | 0.5     | 118.0                          |

|              | 12-bit     | 1       | 117.2                          |              |            | 1       | 156.8                          |

|              |            | 10      | 815.9                          |              |            | 10      | 855.5                          |

|              |            | 20      | 1592.2                         |              |            | 20      | 1631.8                         |

|              |            | 50      | 3921.2                         |              |            | 50      | 3960.8                         |

|              |            | 100     | 7802.8                         |              |            | 100     | 7842.4                         |

|              |            | 0       | 33.9                           |              | 10-bit     | 0       | 67.9                           |

|              |            | 0.05    | 37.3                           | 1            |            | 0.05    | 71.2                           |

|              |            | 0.1     | 40.6                           |              |            | 0.1     | 74.5                           |

| fast channel |            | 0.2     | 47.2                           |              |            | 0.2     | 81.2                           |

|              | 10.1%      | 0.5     | 67.2                           | 1, , ,       |            | 0.5     | 101.1                          |

|              | 10-bit     | 1       | 100.5                          | slow channel |            | 1       | 134.4                          |

|              |            | 10      | 699.4                          |              |            | 10      | 733.3                          |

|              |            | 20      | 1364.8                         |              |            | 20      | 1398.7                         |

|              |            | 50      | 3361.0                         |              |            | 50      | 3395.0                         |

|              |            | 100     | 6688.1                         |              |            | 100     | 6722.1                         |

| fast channel |            | 0       | 28.3                           |              | 8-bit      | 0       | 56.6                           |

|              |            | 0.05    | 31.1                           |              |            | 0.05    | 59.3                           |

|              | 8-bit      | 0.1     | 33.8                           |              |            | 0.1     | 62.1                           |

|              |            | 0.2     | 39.4                           |              |            | 0.2     | 67.7                           |

|              |            | 0.5     | 56.0                           | slow channel |            | 0.5     | 84.3                           |

|              |            | 1       | 83.7                           |              |            | 1       | 112.0                          |

|              |            | 10      | 582.8                          |              |            | 10      | 611.1                          |

|              |            | 20      | 1137.3                         |              |            | 20      | 1165.6                         |

|              |            | 50      | 2800.9                         |              |            | 50      | 2829.1                         |

|              |            | 100     | 5573.5                         |              |            | 100     | 5601.7                         |

|              | 6-bit      | 0       | 22.6                           | slow channel | 6-bit      | 0       | 45.2                           |

|              |            | 0.05    | 24.8                           |              |            | 0.05    | 47.5                           |

|              |            | 0.1     | 27.1                           |              |            | 0.1     | 49.7                           |

| 6 . 1 . 1    |            | 0.2     | 31.5                           |              |            | 0.2     | 54.1                           |

|              |            | 0.5     | 44.8                           |              |            | 0.5     | 67.4                           |

| fast channel |            | 1       | 67.0                           |              |            | 1       | 89.6                           |

|              |            | 10      | 466.2                          |              |            | 10      | 488.9                          |

|              |            | 20      | 909.9                          |              |            | 20      | 932.5                          |

|              |            | 50      | 2240.7                         |              |            | 50      | 2263.3                         |

|              |            | 100     | 4458.8                         |              |            | 100     | 4481.4                         |

Taking the N32G430 series as an example: When using a 12-bit ADC with a sampling clock of 80MHz and an external analog signal input impedance of  $10k\Omega$ , to match the appropriate sampling period, it can be determined from the table that the minimum time is 815.9ns. The corresponding sampling time must be greater than 52.7 cycles (corresponding to the configuration value of ADC\_SAMPT.SAMPx).

Correctly configure the ADC clock

The ADC requires three clocks: the operating clock, the sampling clock, and the counting clock. During ADC initialization, all three clocks need to be correctly configured, as improper configuration can affect the digital values of the signal acquisition conversion.

### 2.6 Small Signal Measurement

When it is necessary to collect mV-level input signals, the following methods can be used:

- Use an external amplification circuit to amplify the small input signal before outputting it to the ADC for acquisition.

- Select the ADC fast channel and increase the ADC sampling period.

- Add a capacitor with appropriate parameters to the input channel.

- Use software oversampling and software filtering to extract the desired values that meet your requirements.

#### 2.7 Differential Calculation Formula

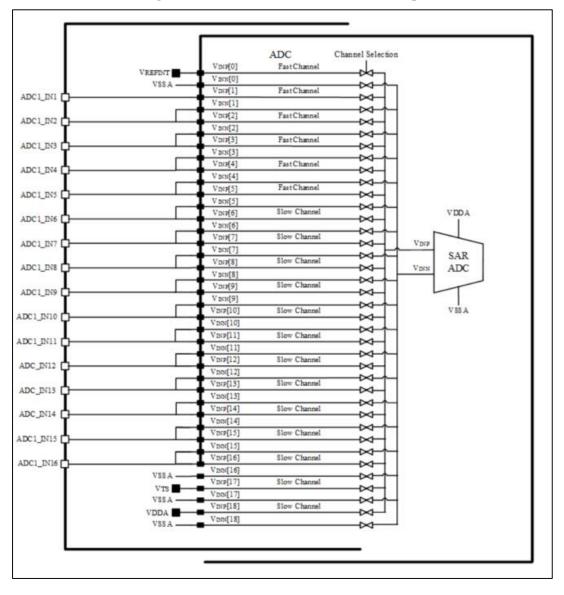

Some series of ADCs support differential inputs, where the positive and negative terminals of the differential input need to be adjacent ADC channels (see Figure 2-14 ADC Channel and PIN Relationship). This can be configured in the ADC\_DIFSEL register for differential mode.

The differential signal input range is between 0 and  $V_{REF}$ , the output range is  $-V_{REF}$  to  $+V_{REF}$ , and the common-mode voltage range is  $\frac{v_{DD}}{2}$ -0.18 $-\frac{v_{DD}}{2}$ +0.18. The conversion value can be calculated as follows: ADC\_DAT = 4095 \*  $(\frac{1}{2}*\frac{v_{in}}{v_{ref}}+\frac{1}{2})$ . Example:

**Table 2-2 Voltage Range**

| ADC_DAT | VINP  | VINN  | VIN   | VREF |

|---------|-------|-------|-------|------|

| 0       | 0V    | 3.3V  | -3.3V | 3.3V |

| 2048    | 1.65V | 1.65V | 0V    | 3.3V |

| 4095    | 3.3V  | 0V    | 3.3V  | 3.3V |

Figure 2-14 ADC Channel and PIN Relationship

## 3. Conclusion

This application note mainly introduces the ADC module, helping users quickly familiarize themselves with the application and configuration of the ADC.

If there are any questions regarding the parameters mentioned in this document, please refer to the product datasheet for accurate information.

# 4. Version History

| Version | Date       | Changes         |

|---------|------------|-----------------|

| V1.0.0  | 2024.05.30 | Initial release |

### 5. Notice

This document is the exclusive property of NSING TECHNOLOGIES PTE. LTD. (Hereinafter referred to as NSING). This document, and the product of NSING described herein (Hereinafter referred to as the Product) are owned by NSING under the laws and treaties of Republic of Singapore and other applicable jurisdictions worldwide. The intellectual properties of the product belong to NSING Technologies Inc. and NSING Technologies Inc. does not grant any third party any license under its patents, copyrights, trademarks, or other intellectual property rights. Names and brands of third party may be mentioned or referred thereto (if any) for identification purposes only. NSING reserves the right to make changes, corrections, enhancements, modifications, and improvements to this document at any time without notice. Please contact NSING and obtain the latest version of this document before placing orders. Although NSING has attempted to provide accurate and reliable information, NSING assumes no responsibility for the accuracy and reliability of this document. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. In no event shall NSING be liable for any direct, indirect, incidental, special, exemplary, or consequential damages arising in any way out of the use of this document or the Product. NSING Products are neither intended nor warranted for usage in systems or equipment, any malfunction or failure of which may cause loss of human life, bodily injury or severe property damage. Such applications are deemed, Insecure Usage'. Insecure usage includes, but is not limited to: equipment for surgical implementation, atomic energy control instruments, airplane or spaceship instruments, all types of safety devices, and other applications intended to supporter sustain life. All Insecure Usage shall be made at user's risk. User shall indemnify NSING and hold NSING harmless from and against all claims, costs, damages, and other liabilities, arising from or related to any customer's Insecure Usage Any express or implied warranty with regard to this document or the Product, including, but not limited to. The warranties of merchantability, fitness for a particular purpose and non-infringement are disclaimed to the fullest extent permitted by law. Unless otherwise explicitly permitted by NSING, anyone may not use, duplicate, modify, transcribe or otherwise distribute this document for any purposes, in whole or in part.