# N32G43X & N32L40X & N32L43X系列硬件设计指南

简介

本文档详细介绍 N32G43X/N32L40X/N32L43X 系列 MCU 硬件设计检查列表,以便为用户提供硬件设计指导。

国民技术 版权所有

# 目录

| 1. | N32G43X/ | 'N32L40X/ N32L43X 系列 MCU 硬件设计检查列表 | 1  |

|----|----------|-----------------------------------|----|

|    | 1.1      | 电源供电简介                            | 1  |

|    | 1.2      | 供电方案                              | 1  |

|    | 1.3      | 外部引脚复位电路                          | 1  |

|    | 1.4      | 外部时钟电路                            | 1  |

|    | 1.5      | 启动引脚连接                            | 2  |

|    | 1.6      | 独立 ADC 转换器                        | 2  |

|    | 1.7      | IO 上电脉冲处理                         | 5  |

|    | 1.8      | IO 耐压值                            | 6  |

|    | 1.9      | 防静电设计                             | 6  |

|    | 1.9.1    | PCB 设计                            | 6  |

|    | 1.9.2    | ESD 防护器件                          | 6  |

|    | 1.10     | 调试接口                              | 7  |

|    | 1.11     | BOOT 串口接口                         | 7  |

| 2. | 整体设计     | 建议                                | 8  |

| 3. | 最小系统参    | <b>参考设计原理图</b>                    | 9  |

|    | 3.1      | LQFP80                            | 9  |

|    | 3.2      | LQFP64                            | 10 |

|    | 3.3      | LQFP48                            | 11 |

|    | 3.4      | LQFP32                            | 12 |

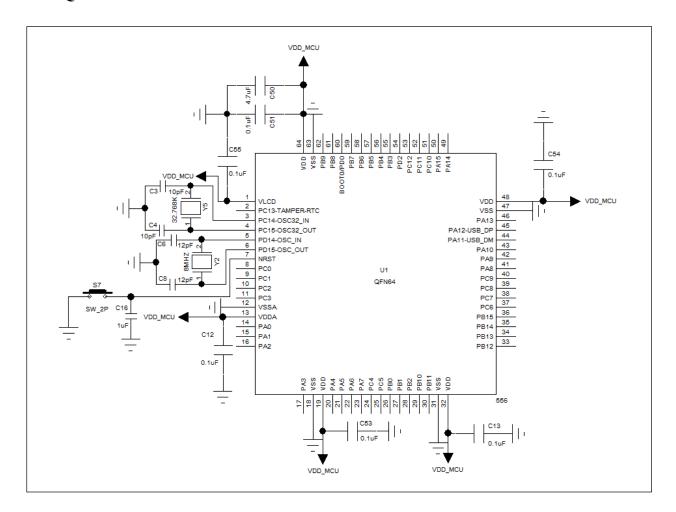

|    | 3.5      | QFN64                             | 13 |

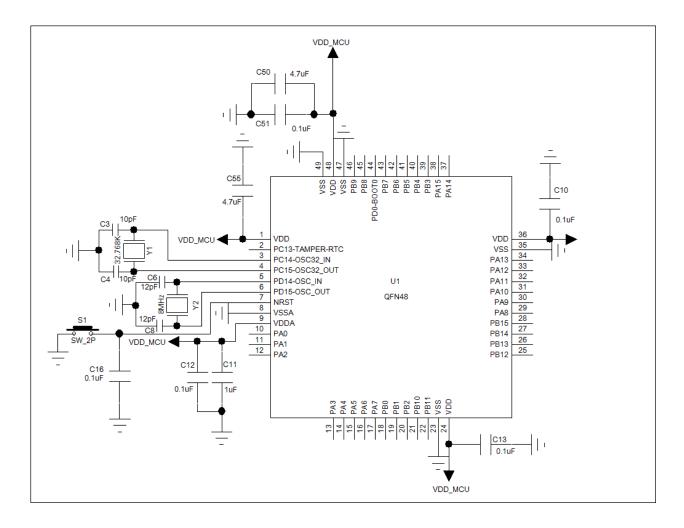

|    | 3.6      | QFN48                             | 14 |

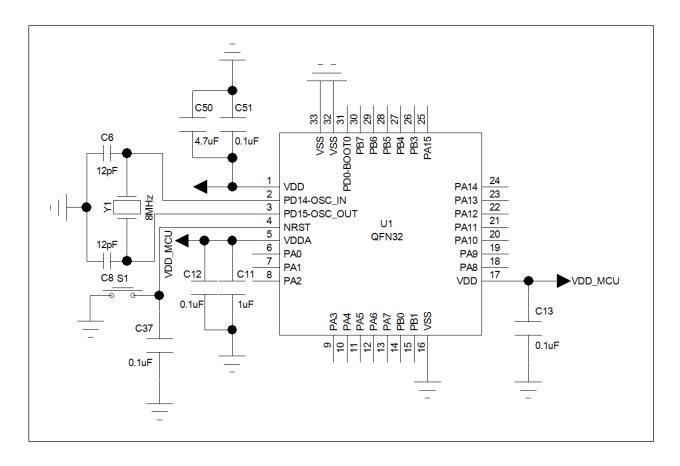

|    | 3.7      | QFN32                             | 15 |

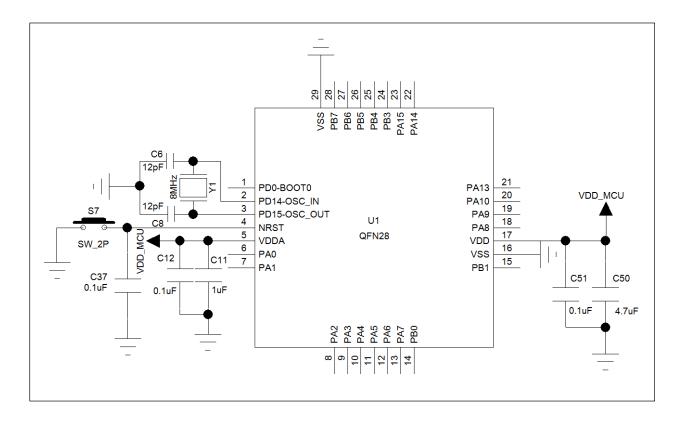

|    | 3.8      | QFN28                             | 16 |

| 4. | PCB LAY  | OUT 参考                            | 17 |

| 5. | 典型故障分    | 分析                                | 18 |

|    | 5.1      | 电源管脚与地短路                          | 18 |

|    | 5.2      | GPIO 损坏                           | 18 |

|    | 5.3      | ADC 采样不准                          | 18 |

| 6. | 历史版本.    |                                   | 19 |

| 7. | 声 明      |                                   | 20 |

## 1. N32G43X/N32L40X/ N32L43X 系列 MCU 硬件设计检查列表

### 1.1 电源供电简介

N32G43X/N32L40X/ N32L43X 系列芯片工作电压(VDD)为 1.8V~3.6V。主要有: VDD、VDDA 引脚。具体请参考相关数据手册。

## 1.2 供电方案

VDD 为 MCU 主电源,必须由稳定的外部电源供电。电压范围 1.8V~3.6V,所有 VDD 引脚都需就近放置一颗 0.1uF 去耦电容,其中一个 VDD 管脚还需增加一颗 4.7uF 去耦电容。去耦电容具体设计请参考第三章节各封装最小系统参考设计原理图.

VDDA 为模拟电源,为 ADC、DAC、OPAMP、COMP 提供供电。VDDA 输入管脚建议放置一个 0.1uF 和一个 1uF 的电容。

### 1.3 外部引脚复位电路

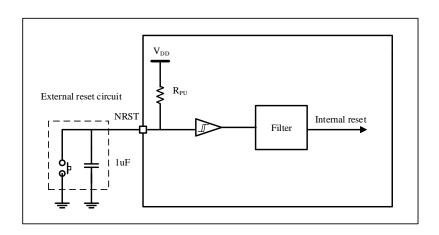

当NRST引脚上出现低电平(外部复位)将产生系统复位。外部NRST引脚复位参考电路如下。

图 1-1 系统复位图

注:复位引脚NRST在设计时不能悬空,外挂电容1uF作为典型参考值给出,若需加快复位时间,NRST引脚可外加上拉,上拉电阻典型值10K,另外用户可根据产品实际需要决定是否增加复位按键。

## 1.4 外部时钟电路

N32G43X/N32L40X/ N32L43X 系列 MCU 包含 2 个外部时钟: 外部高速时钟 HSE(4MHz~32MHz)和 外部低速时钟 LSE(通常使用 32.768KHz)。

HSE 和 LSE 根据晶振特性配置相应的负载电容,详细请参考相关数据手册中外部时钟特性描述。

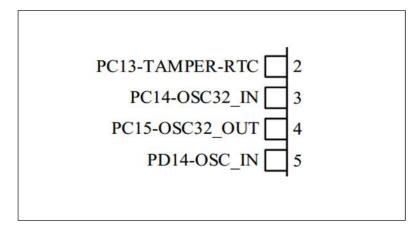

在使用 LSE 时,相邻的 IO 管脚(PC13 和 PD14)不能有 GPIO 翻转电平信号,邻近管脚参考图 1-2。翻转的电平信号会导致 LSE 工作不稳定。

图 1-2 PC13/PD14 管脚不能有翻转信号

### 1.5 启动引脚连接

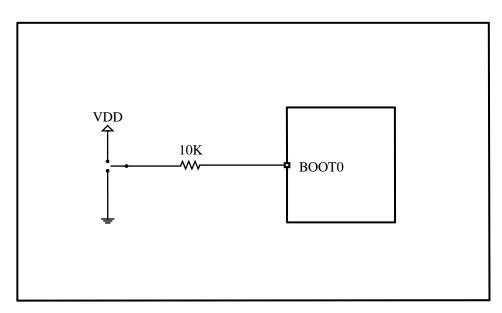

下图显示了 N32G43X/N32L40X/ N32L43X 系列芯片选择启动存储器时所需的外部连接。关于启动模式请参考数据手册相关章节。

图 1-3 启动模式实现实例

BOOT引脚拉高,芯片复位后从BOOT区启动;BOOT引脚拉低,芯片复位后从用户区启动。 注:图中电阻值只作为典型参考值给出。

## 1.6 独立 ADC 转换器

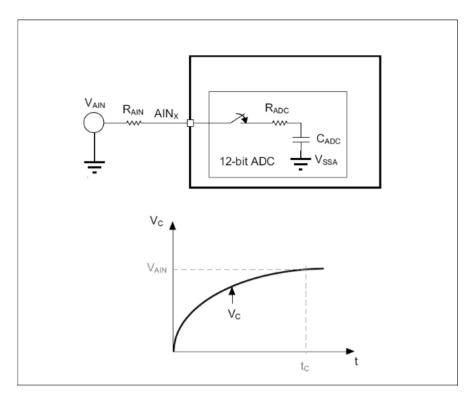

为提高转换精度,ADC 有一对独立的供电电源,一个独立的 VDDA 引脚给 ADC 供电,VSSA 引脚作为模拟供电的接地端,它可以被单独滤波和屏蔽后给 ADC 供电,以减少 PCB 板级噪音的干扰。

关于 ADC 电路设计,请注意如下几点:

1) 在使用 ADC 采样时,建议缩短 ADC 采样通道的外部走线距离;

- 2) ADC 的输入信号周边建议远离一些高频翻转信号;

- 3) 注意慢速通道和快速通道的最高支持速率:

N32G43x\_L43x 系列在输入主频为 72MHZ 条件下, ADC 快速通道采样率不超过 5Msps, ADC 慢速通道采样率建议不超过 2.5Msps;

N32L40x 系列在输入主频为 64MHZ 条件下,ADC 快速通道采样率不超过 4.5Msps,ADC 慢速通道采样率建议不超过 2Msps。

- 4) 在 ADC 转换期间,芯片不支持修改 ADC 配置,如需修改配置,需要等待当前转换结束或者关闭 ADC 后,再进行配置;

- 5) 在使用某一 ADC 通道时,不能在其它未使用的 ADC 采样通道施加负压(比如-0.2V),如果施加了此负电压,会导致正常采样的 ADC 通道电压被拉低,导致读取的数据不准;

- 6) 在使用 ADC 时, R<sub>AIN</sub> 的最大值不能太大, 需要符合如下公式:

$$R_{\text{AIN}} < \frac{T_{\text{S}}}{f_{\text{ADC}} \times C_{\text{ADC}} \times \ln(2^{N+2})} - R_{\text{ADC}}$$

图 1-4 ADC 输入口串联电阻的影响

下图为典型输入阻抗下 ADC 采样配置规则表:

| ADC工作时钟频率: 72MHz   |              |                          |                                          |                        |  |

|--------------------|--------------|--------------------------|------------------------------------------|------------------------|--|

| 输入等效阻抗<br>R_AIN(Ω) | Min Sampling | Min Sampling<br>Time(ns) | ADC<br>Sampleing+<br>Convert<br>Time(us) | ADC<br>最大采样率<br>(Ksps) |  |

| 0                  | 1. 75        | 24. 26                   | 0. 198                                   | 5, 053. 8              |  |

| 100                | 2. 10        | 29. 11                   | 0. 203                                   | 4, 932. 8              |  |

| 330                | 2. 90        | 40. 27                   | 0. 214                                   | 4, 675. 5              |  |

| 470                | 3. 39        | 47.06                    | 0. 221                                   | 4, 531. 5              |  |

| 1,000              | 5. 24        | 72. 78                   | 0. 246                                   | 4, 058. 6              |  |

| 2, 200             | 9. 43        | 131. 00                  | 0. 305                                   | 3, 282. 8              |  |

| 4, 700             | 18. 17       | 252. 31                  | 0. 426                                   | 2, 347. 9              |  |

| 10,000             | 36. 68       | 509. 46                  | 0. 683                                   | 1, 464. 0              |  |

| 30,000             | 106. 55      | 1, 479. 87               | 1. 653                                   | 604. 8                 |  |

| 51,000             | 179. 91      | 2, 498. 80               | 2. 672                                   | 374. 2                 |  |

| 100, 000           | 351. 09      | 4, 876. 29               | 5. 050                                   | 198. 0                 |  |

| 470,000            | 1, 643. 67   | 22, 828. 80              | 23. 002                                  | 43. 5                  |  |

| 1,000,000          | 3, 495. 21   | 48, 544. 56              | 48. 718                                  | 20. 5                  |  |

图 1-5 N32G43x \_L43x 系列 ADC 采样配置规则表

| ADC工作时钟频率: 64MHz   |                       |                          |                                          |                        |  |

|--------------------|-----------------------|--------------------------|------------------------------------------|------------------------|--|

| 输入等效阻抗<br>R_AIN(Ω) | Min Sampling<br>cycle | Min Sampling<br>Time(ns) | ADC<br>Sampleing+<br>Convert<br>Time(us) | ADC<br>最大采样率<br>(Ksps) |  |

| 0                  | 1.55                  | 24. 26                   | 0.220                                    | 4,554.3                |  |

| 100                | 1.86                  | 29.11                    | 0.224                                    | 4,455.8                |  |

| 330                | 2.58                  | 40.27                    | 0.236                                    | 4,244.8                |  |

| 470                | 3.01                  | 47.06                    | 0.242                                    | 4,125.8                |  |

| 1,000              | 4.66                  | 72. 78                   | 0.268                                    | 3,730.0                |  |

| 2, 200             | 8. 38                 | 131.00                   | 0.326                                    | 3,064.5                |  |

| 4,700              | 16.15                 | 252. 31                  | 0.448                                    | 2, 234. 0              |  |

| 10,000             | 32.61                 | 509.46                   | 0.705                                    | 1,418.9                |  |

| 30,000             | 94. 71                | 1,479.87                 | 1.675                                    | 597.0                  |  |

| 51,000             | 159. 92               | 2, 498. 80               | 2.694                                    | 371.2                  |  |

| 100,000            | 312.08                | 4,876.29                 | 5.072                                    | 197.2                  |  |

| 470,000            | 1,461.04              | 22,828.80                | 23.024                                   | 43.4                   |  |

| 1,000,000          | 3,106.85              | 48,544.56                | 48.740                                   | 20.5                   |  |

图 1-6 N32L40x 系列 ADC 采样配置规则表

注:采样时间需根据输入时钟和ADC寄存器可选的采样周期综合配置,原则上ADC采样周期配置应大于等于表中最小采样周期数。

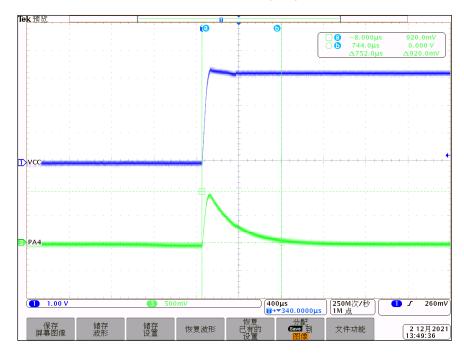

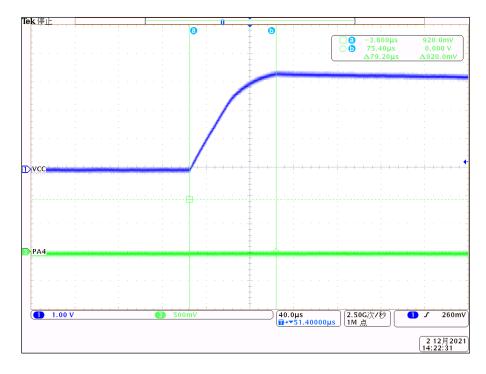

### 1.7 IO 上电脉冲处理

上电过程中由于 IO 处于高阻态及内部电路耦合特性,上电瞬间会引起 IO 上出现高电平脉冲(实际的高脉冲电压值请用户实测)。若该脉冲会影响其应用,建议在对应 IO 上挂适当电容(1nF~100nF)或外加适当下拉电阻(10K~100K)处理。

下图为开发板 N32G43XRL-STB V1.0 上电过程中 IO(PA4)波形图:

图 1-7 上电过程 IO(PA4)波形

下图为开发板 N32G43XRL-STB V1.0 上电过程中 IO(PA4)外加 10K 下拉电阻后的波形图:

图 1-8 上电过程 IO (PA4) 外加下拉电阻处理后波形

### 1.8 IO 耐压值

芯片使用时请注意各 IO 耐压值,在数据手册引脚复用定义的 I/O 结构一栏,标注了 TTa: 3.3V standard IO, 这类型 IO 在与外部其它不同电压域的 IO 进行通讯时,需要做电平转换。

|       | 封装     |        |        |                                 |       | 电平②   | E. 7                               | 可选的复用功能(3)            |                               |

|-------|--------|--------|--------|---------------------------------|-------|-------|------------------------------------|-----------------------|-------------------------------|

| QFN28 | LQFP32 | LQFP48 | LQFP64 | 管脚名称(复位后)                       | 类型(1) | I/O 电 | Fail-<br>safe <sup>(5)</sup><br>支持 | 复用功能                  | 可选功能                          |

| -     | 1      | 1      | 1      | VDD                             | S     | -     | -                                  | -                     | -                             |

| -     | -      | 2      | 2      | PC13-TAMPER- RTC <sup>(4)</sup> | I/O   | ТТа   | Yes                                | TIM1_CH1N<br>EVENTOUT | TAMP1-RTC<br>RTC_OUT<br>WKUP2 |

| -     | -      | 3      | 3      | PC14- OSC32_IN <sup>(4)</sup>   | I/O   | TTa   | Yes                                | -                     | OSC32_IN                      |

| -     | -      | 4      | 4      | PC15- OSC32_OUT <sup>(4)</sup>  | I/O   | TTa   | Yes                                | •                     | OSC32_OUT                     |

图 1-9 数据手册引脚复用定义的 I/O 结构

注: TTa: 3.3V standard IO。在使用芯片时需注意高于 3.3V 的信号对 IO 的影响。

### 1.9 防静电设计

### 1.9.1 PCB 设计

对于普通两层板的 PCB 设计,建议信号线周围做包地处理,PCB 板边也尽量做到铺地环绕。在成本允许的条件下,可以用四层板或多层板设计,在多层 PCB 中地线面作为一个重要的电荷源,可抵消静电放电源上的电荷,这有利于减小静电场带来的问题。PCB 地线面也可作为其对信号线的屏蔽体(当然,地线面的开口越大,其屏蔽效能就越低)。另外,如果发生放电,由于 PCB 板的地平面很大,电荷很容易注入到地线面中,而不是进入到信号线中。这样将有利于对元件进行保护,因为在引起元件损坏前,电荷可以泄放掉。

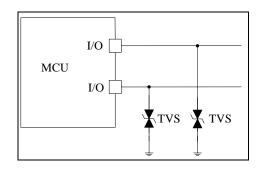

## 1.9.2 ESD 防护器件

在实际产品设计中,有些芯片的管脚需要直接外接作为产品的输出或输入口,此时,芯片的管脚就直接暴露在产品的最外面,不能通过铺地等方式进行隔离。这种条件下,一般需要考虑外加 ESD 防护器件,TVS 管是一种典型的 ESD 保护器件,以下是典型的连接方式示例。

图 1-10 I/O 管脚上 TVS 连接方式

## 1.10 调试接口

N32G43X/N32L40X/N32L43X 系列芯片支持串行接口(SWD)和 JTAG 调试接口,详细应用请参考相关用户手册。

| 调试信号       | GPIO 引脚 |

|------------|---------|

| JTMS/SWDIO | PA13    |

| JTCK/SWCLK | PA14    |

| JTDI       | PA15    |

| JTDO       | PB3     |

| JNTRST     | PB4     |

表 1-1 调试接口

## 1.11 BOOT 串口接口

N32G43X/N32L40X/N32L43X 系列芯片支持 BOOT 串口通讯, 串口接口如下表:

| BOOT 串口   | GPIO 引脚 |

|-----------|---------|

| USART1_TX | PA9     |

| USART1_RX | PA10    |

表 1-2 串口接口

## 2. 整体设计建议

#### 1) 印制电路板

建议使用有专门独立的接地层(VSS)和专门独立的供电层(VDD)的多层印制电路板,从而能提供好的耦合性能和屏蔽效果。在实际应用中,如考虑成本因素不能使用多层印制电路板,那么在设计电路时就需保证一个好的接地和供电的结构。

#### 2) 器件位置

在 PCB 设计时根据各器件对 EMI 影响的不同,需把不同的电路分开布局。比如,大电流电路、低电压电路、以及高频器件等。从而减少 PCB 上的交叉耦合。

#### 3) 接地和供电(VSS, VDD)

各模块(模拟电路、数字电路、敏感度低的电路)都应该单独接地,数字地和模拟地分开,所有的地最终都应在一个点上连到一起。根据印制线路板电流的大小,尽量加粗电源线宽度,减少环路电阻。同时,电源线、地线的走向和电流的方向应尽量一致,且电源应尽量靠近地线,减小回路的区域。这样有助于增强抗噪声能力。PCB上没有器件的区域,需要填充为地,以提供好的屏蔽效果。

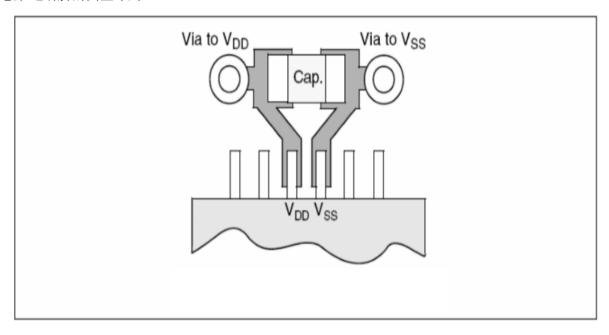

#### 4) 去耦合

所有的电源引脚都需要适当的连接到电源。这些连接,包括焊盘、连线和过孔应该具备尽量小的阻抗。通常采用增加连线宽度的办法,同时每对 VDD 与 VSS 引脚都必须在靠近芯片处放置去耦电容。下图为电源/地引脚的典型布局。

图 2-1 VDD/VSS 引脚的典型布局

## 3. 最小系统参考设计原理图

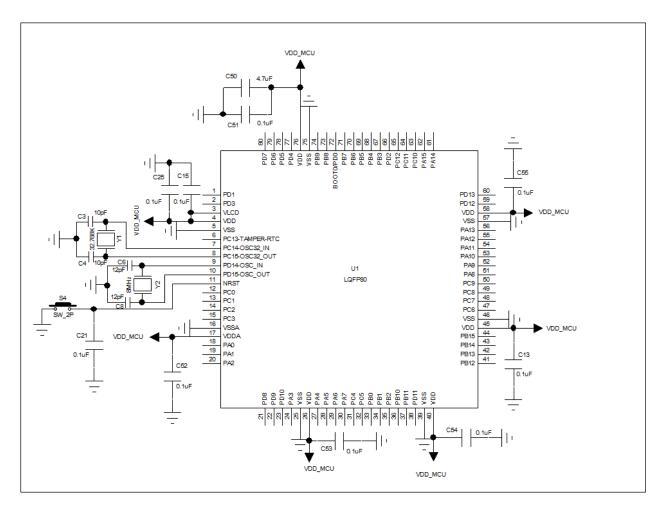

## 3.1 LQFP80

图 3-1 LQFP80 封装最小系统参考设计原理图

电话: +86-755-86309900 传真: +86-755-86169100 邮箱: info@nationstech.com 邮编: 518057

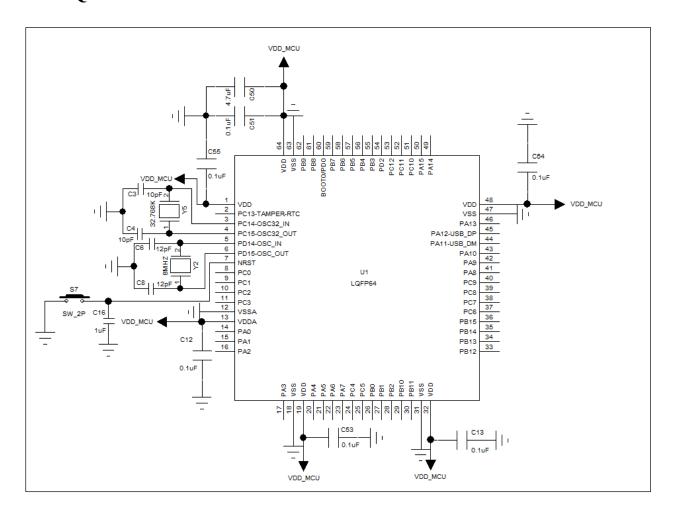

## 3.2 LQFP64

图 3-2 LQFP64 封装最小系统参考设计原理图

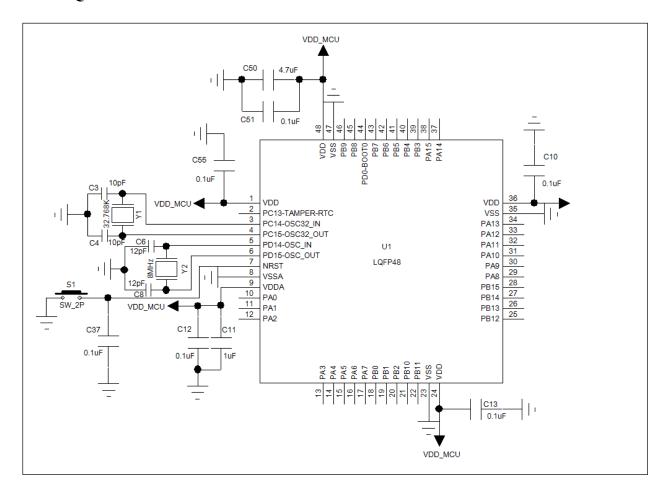

## 3.3 LQFP48

图 3-3 LQFP48 封装最小系统参考设计原理图

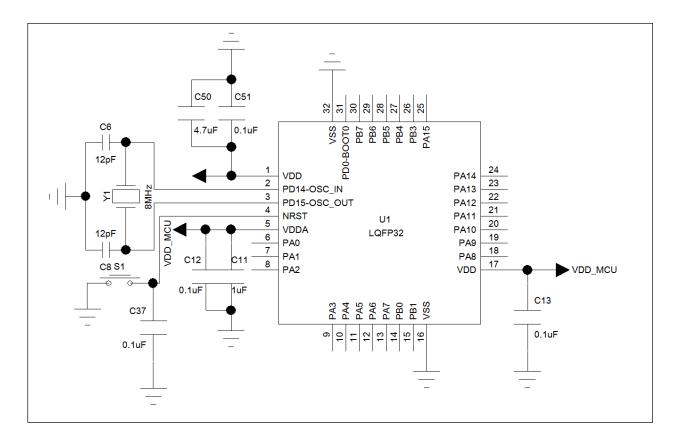

## 3.4 LQFP32

图 3-4 LQFP32 封装最小系统参考设计原理图

## 3.5 QFN64

图 3-5 QFN64 封装最小系统参考设计原理图

## 3.6 QFN48

图 3-6 QFN48 封装最小系统参考设计原理图

## 3.7 QFN32

图 3-7 QFN32 封装最小系统参考设计原理图

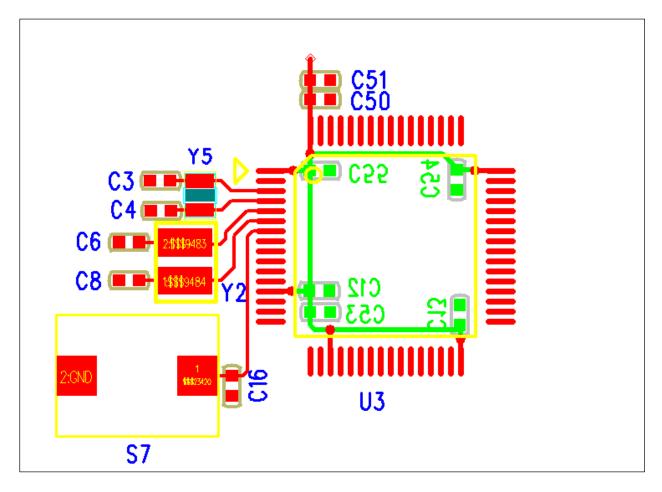

### 3.8 QFN28

图 3-8 QFN28 封装最小系统参考设计原理图

图 3-1~图 3-8 是 N32G43X/N32L40X/ N32L43X 系列各封装最小系统参考设计原理图,主要体现供电电源去耦电容、时钟、复位电路等设计,其中时钟电路取决于用户设计,芯片内部支持内部高速和低速时钟可供用户选择。

# 4. PCB LAYOUT 参考

图 4-1 LQFP64 封装 PCB LAYOUT 参考图

PCB LAYOUT 设计时,每一个电源管脚都需要就近放置去耦电容。HSE 和 LSE 的外部晶体及走线尽可能在周围做包地处理,晶体下面一层靠近晶体的区域也需要铺地,不能有信号线穿过,防止信号线干扰晶体信号。

## 5. 典型故障分析

针对客户在使用芯片过程中遇到的常见问题和分析方法说明如下。

### 5.1 电源管脚与地短路

#### 问题描述:

芯片 VDD 管脚与 GND 测试短路,芯片上电后异常发热。

#### 问题检查:

- 1) VDD 去耦电容是否耐压值不够导致电容击穿短路。

- 2) 产品启动时, VDD 电压是否有超过规定的最大值。

- 3) 产品在运行过程中,是否有超过 VDD 最大值的过冲电压

- 4) 生产和使用过程中,是否有静电导致芯片损坏。

### 5.2 GPIO 损坏

#### 问题描述:

芯片 GPIO 不能正常输出高电平或低电平,GPIO 作为输入检测电平错误,VIH 或 VIL 测试值异常,管脚阻抗异常。

#### 问题检查:

- 1) 芯片 GPIO 输出电压是否超过最大值,比如 3.3V的 I/O 输入了 5V 的电压。

- 2) 产品生产和测试过程中,是否存在高压输入到 GPIO 口。

- 3) 产品设计上, GPIO 走线附近是否存在高压信号耦合到 GPIO 输入口。

- 4) 生产和使用过程中,是否有静电导致芯片损坏。

## 5.3 ADC 采样不准

#### 问题描述:

芯片 ADC 输入口采样电压时,采样电压不准。

#### 问题检查:

参考 1.6 章节,确认是否软硬件设置符合 ADC 注意事项的要求。

# 6. 历史版本

| 版本   | 日期         | 备注                                                                                                                                                                                      |  |

|------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| V1.0 | 2020-12-24 | 创建文档                                                                                                                                                                                    |  |

| V1.1 | 2022-2-27  | 1、修改 1.4 外部时钟电路章节 (新增 LSE 使用注意事项) 2、增加 1.5 启动引脚连接章节 3、修改 1.6 独立 ADC 转换器章节 (ADC 使用注意事项修改) 4、增加 1.7 IO 口上电脉冲处理章节 5、增加 1.8 IO 口耐压值章节 6、增加 1.9 防静电设计章节 7、增加 1.10 调试接口章节 8、增加 1.11 BOOT 串口章节 |  |

|      |            | 9、增加典型故障分析第5章节                                                                                                                                                                          |  |

## 7. 声明

国民技术股份有限公司(下称"国民技术")对此文档拥有专属产权。依据中华人民共和国的法律、条约以及世界其他法域相适用的管辖,此文档及其中描述的国民技术产品(下称"产品")为公司所有。

国民技术在此并未授予专利权、著作权、商标权或其他任何知识产权许可。所提到或引用的第三方名称或品牌(如有)仅用作区别之目的。

国民技术保留随时变更、订正、增强、修改和改良此文档的权利,恕不另行通知。请使用人在下单购买前联系国民技术获取此文档的最新版本。

国民技术竭力提供准确可信的资讯,但即便如此,并不推定国民技术对此文档准确性和可靠性承担责任。

使用此文档信息以及生成产品时,使用者应当进行合理的设计、编程并测试其功能性和安全性,国民技术不对任何因使用此文档或本产品而产生的任何直接、间接、意外、特殊、惩罚性或衍生性损害结果承担责任。

国民技术对于产品在系统或设备中的应用效果没有任何故意或保证,如有任何应用在其发生操作不当或故障情况下,有可能致使人员伤亡、人身伤害或严重财产损失,则此类应用被视为"不安全使用"。

不安全使用包括但不限于: 外科手术设备、原子能控制仪器、飞机或宇宙飞船仪器、所有 类型的安全装置以及其他旨在支持或维持生命的应用。

所有不安全使用的风险应由使用人承担,同时使用人应使国民技术免于因为这类不安全使 用而导致被诉、支付费用、发生损害或承担责任时的赔偿。

对于此文档和产品的任何明示、默示之保证,包括但不限于适销性、特定用途适用性和不 侵权的保证责任,国民技术可在法律允许范围内进行免责。

未经明确许可,任何人不得以任何理由对此文档的全部或部分进行使用、复制、修改、抄录和传播。