# **Application** Note

# N32G45x&N32G4FR&N32WB452 Series Low Power Application

## Note

#### Introduction

In the embedded product development process, it is sometimes necessary to use the battery scenario, in this scenario, it is expected that the battery can maintain a longer service life, so the low power setting is necessary.

This document mainly aims at the above application scenarios of NATIONS MCU series products, and instructs users how to use the MCU, and realize the control of battery power consumption by implementing the MCU into different low-power modes through the PWR module.

The N32G45x, N32G4FR, N32WB452 series integrate the latest generation of embedded ARM Cortex<sup>TM</sup>-M4F processor, based on the Cortex<sup>TM</sup>-M3 core enhanced computing power, new float point unit (FPU), DSP and parallel computing instructions. Provides excellent performance of 1.25DMIPS/MHz. Its efficient signal processing capabilities are combined with the advantages of low power consumption, low cost, and ease of use of the Cortex-M family of processors to meet the requirements of a mixture of control and signal processing capabilities and easy to use applications.N32G45x, N32G4FR, N32WB452 have five low-power operation modes (SLEEP mode, STOP0 mode, STOP2 mode, STANDBY mode, VBAT mode), the user should choose the best low-power mode according to power consumption, short startup time and available wake-up source.

# **All Rights Reserved**

I

# Contents

| Co | ContentsII |                                         |  |  |  |

|----|------------|-----------------------------------------|--|--|--|

| 1  | Low        | power operation mode1                   |  |  |  |

|    | 1.1        | SLEEP mode1                             |  |  |  |

|    | 1.1.1      | Enter SLEEP mode1                       |  |  |  |

|    | 1.1.2      | Exit SLEEP mode1                        |  |  |  |

|    | 1.2        | STOP0 mode1                             |  |  |  |

|    | 1.2.1      | Enter STOP0 mode2                       |  |  |  |

|    | 1.2.2      | Exit STOP0 mode2                        |  |  |  |

|    | 1.3        | STOP2 mode2                             |  |  |  |

|    | 1.3.1      | Enter STOP2 mode2                       |  |  |  |

|    | 1.3.2      | Exit STOP2 mode3                        |  |  |  |

|    | 1.4        | STANDBY mode                            |  |  |  |

|    | 1.4.1      | Enter STANDBY mode                      |  |  |  |

|    | 1.4.2      | Exit STANDBY mode4                      |  |  |  |

|    | 1.5        | VBAT mode4                              |  |  |  |

|    | 1.5.1      | Enter VBAT mode                         |  |  |  |

|    | 1.5.2      | Exit VBAT mode                          |  |  |  |

| 2  | Powe       | er control (PWR)4                       |  |  |  |

|    | 2.1        | Power system introduction               |  |  |  |

|    | 2.1.1      | Power supply5                           |  |  |  |

|    | 2.1.2      | Backup power domain6                    |  |  |  |

|    | 2.2        | Supply current characteristic           |  |  |  |

|    | 2.2.1      | General operating conditions7           |  |  |  |

|    | 2.2.2      | Maximum current consumption8            |  |  |  |

|    | 2.2.3      | Typical current consumption10           |  |  |  |

| 3  | Hard       | lware environment12                     |  |  |  |

|    | 3.1        | Development board layout                |  |  |  |

|    | 3.2        | Development board jumper instructions14 |  |  |  |

|    | 3.3        | Development board schematic diagram15   |  |  |  |

| 4  | Prog       | ramming instructions                    |  |  |  |

|    | 4.1        | Set SLEEP mode                          |  |  |  |

|    | 4.2        | Set STOP2 mode17                        |  |  |  |

|    | 4.3        | Set STOP0 mode17                        |  |  |  |

|    | 4.4        | Set STANDBY mode                        |  |  |  |

| 5  | Versi      | on history20                            |  |  |  |

| 6  | Lega       | l Notice21                              |  |  |  |

# **1** Low power operation mode

## 1.1 **SLEEP mode**

In SLEEP mode, only the CPU stops and all peripherals are active and can wake up the CPU in the event of an interrupt/event.

### 1.1.1 Enter SLEEP mode

Enter SLEEP mode by executing the WFI (wait interrupt) or WFE (wait event) command and SLEEPDEEP = 0. Based on the value of the SLEEPONEXIT bit in the Cortex®-M4 system control register, there are two options for selecting the SLEEP mode entry mechanism:

- Sleep-now: If SLEEPONEXIT is cleared, the WFI or WFE command will execute immediately and the system will enter SLEEP mode immediately.

- Sleep-on-exit: If SLEEPONEXIT is set, the system enters SLEEP mode as soon as it exits from the lowestpriority interrupt handler.

In SLEEP mode, all I/O pins remain in the same state/function as in run mode.

## 1.1.2 Exit SLEEP mode

If you enter SLEEP mode using the WFI command, then any peripheral interrupts responded to by the nested vector interrupt controller (NVIC) can wake the device from SLEEP mode.

If you enter SLEEP mode using the WFE command, the device will exit SLEEP mode as soon as the event occurs. Wake up events can be generated in the following ways:

- Enable an interrupt in the peripheral control register, not in NVIC, and the SEVONPEND bit in the Cortex®-M4 system control register. When MCU recovers from WFE, the peripheral interrupt suspend bit and the peripheral NVIC interrupt channel suspend bit (in the NVIC Interrupt clear suspend register) must be cleared.

- Configure an external or internal EXTI event mode so that when the CPU recovers from WFE, the peripheral interrupt suspend bit and the peripheral NVIC interrupt channel suspend bit (in the NVIC Interrupt clear suspend register) need not be cleared because the suspend bit corresponding to the event line has not been set. This mode provides the shortest wake up time since no time is lost on interrupted entry or exit.

# 1.2 **STOP0 mode**

STOP0 mode is based on the Cortex®-M4 deep sleep mode, combined with the peripheral clock control mechanism. The voltage regulator can be configured for normal or low power mode. In STOP0 mode, most clock sources in the core domain, such as PLL, HSI, and HSE, are disabled. But SRAM, R-SRAM, and all register contents are saved. In STOP0 mode, all I/O pins remain in the same state as in run mode.

1/21

## 1.2.1 Enter STOP0 mode

When entering STOP0 mode, the main difference is to set SLEEPDEEP= 1, PDS=0.Another difference is that MR can be run in normal mode or low power mode by configuring the register PWR\_CTRL bit LPS. When LPS = 1, MR runs in low power mode. When LPS = 0, MR runs in normal mode. In STOP0 mode, all I/O pins remain in the same state and function as in run mode. If FLASH operations are in progress, the entry into STOP0 mode will be delayed until memory access is complete. If access to the APB area is in progress, entering STOP0 mode will be delayed until the APB access is complete. In STOP0 mode, the following features can be selected by programming the individual control bits:

- Independent watchdog (IWDG): Independent watchdog is started when software writes or hardware operations are performed on its associated registers. Once started, it works until a reset message is generated

- RTC: this can be enabled by the RTCEN bit in register RCC\_BDCTRL

- Internal RC oscillator (LSI RC): can be turned on by the LSIEN bit in register RCC\_CTRLSTS

- External 32.768khz crystal oscillator (LSE OSC): Can be turned on by the LSEEN bit in register RCC\_BDCTRL

- ADC or DAC can also consume power in STOP0 mode. ADC and DAC can be disabled before entering STOP0 mode.

Note: If your application needs to disable the external clock before entering stop mode, you must first disable the HSEEN bit and then switch the system clock to HSI. Otherwise, if the HSEEN bit remains enabled when entering stop mode and the external clock (external oscillator) is removed, the Clock Safety System (CSS) feature must be enabled to detect any external oscillator failure and avoid failure behavior when entering stop mode.

### 1.2.2 Exit STOP0 mode

When an interrupt or wake up event exits STOP0 mode, the HSI RC oscillator is selected as the system clock.

When the voltage regulator is operating in low power mode, there is an additional startup delay when awakened from STOP0 mode. In STOP0 mode, if the internal regulator is in normal mode, which can reduce the startup time, but the corresponding power consumption will increase.

## 1.3 STOP2 mode

STOP2 mode is based on the Cortex-M4 deep sleep mode, and all the core digital logic areas are powered off. Main voltage regulator (MR) is off, HSE/HSI/PLL is off. CPU registers are maintained, LSE/LSI can be configured, GPIO is remained, and peripheral I/O multiplexing is not remained.16K bytes of R-SRAM remain, and other SRAM and register data are lost.84-byte backup register hold. GPIO and EXTI are enabled.

### 1.3.1 Enter STOP2 mode

When entering STOP2 mode. The main difference is to set SLEEPDEEP= 1, PWR\_CTRL2.STOP2S =1, PWR\_CTRL bit PDS=0, LPS=0.

In STOP2 mode, if an operation is being performed on FLAH, the time to enter STOP2 mode is delayed until memory

2/21

access is complete.

If access to the APB area is in progress, entering STOP2 mode will be delayed until the APB access is complete.

In STOP2 mode, the following features can be selected by programming the individual control bits:

- Independent watchdog: Independent watchdog is started during software writing or hardware operation of its associated register, and once started will work until a reset message is generated

- RTC: this can be enabled by the RTCEN bit in register RCC\_BDCTRL

- Internal RC oscillator (LSI RC): can be turned on by the LSIEN bit in register RCC\_CTRLSTS

- External 32.768khz crystal oscillator (LSE OSC): Can be turned on by the LSEEN bit in register RCC\_BDCTRL

Note: If you want to keep data (global variables, stacks, etc.) in STOP2, you should put it in R-SRAM.

### **1.3.2 Exit STOP2 mode**

When exiting STOP2 mode by issuing interrupt or wake up events, select the HSI RC oscillator as the system clock. When STOP2 exits, the code resumes execution from where it left off.

### 1.4 **STANDBY mode**

The STANDBY mode achieves lower power consumption and is based on the Cortex®-M4 deep sleep mode. The core area is completely shut down and the backup area is turned on to power the VDD and BKR.

### 1.4.1 Enter STANDBY mode.

Enter STANDBY mode. The main difference is that the Settings SLEEPDEEP= 1, PDS=1.

In STANDBY mode, all I/O pins remain in the high resistance state except NRST, PA0\_WKUP, PC13\_TAMPER, PC14, and PC15.

If you are operating on FLAH, the time to enter STANDBY mode will be delayed until the memory access is complete.

If access to the APB area is in progress, entering STANDBY mode will be delayed until the APB access is complete.

In STANDBY mode, you can program each control bit to select the following features:

- Independent watchdog: Independent watchdog is activated during software writing or hardware operation of its related registers, and once activated, it always works

- Until a reset message is generated

- RTC: this can be enabled by the RTCEN bit in register RCC\_BDCTRL

- Internal RC oscillator (LSI RC): can be turned on by the LSIEN bit in register RCC\_CTRLSTS

- External 32.768khz crystal oscillator (LSE OSC): Can be turned on by the LSEEN bit in register RCC\_BDCTRL

- R-SRAM data retention can be enabled by the SR2STBRET bit in register PWR\_CTRL2

# 1.4.2 Exit STANDBY mode

The device exits STANDBY mode when an external reset (NRST pin), IWDG reset, WKUP pin rise edge, or RTC alarm event rise edge occurs. All registers except the power control status register (PWR\_CTRLSTS) are reset upon awakening from the STANDBY state.

After waking up from STANDBY mode, code execution is the same as after a reset (boot pins are fired, reset vectors are read, and so on). The SBF status flag in the power control status register (PWR\_CTRLSTS) indicates that the MCU exits from standby mode.

# 1.5 **VBAT mode**

In VBAT mode the CPU is off, all peripherals are off, the main voltage regulator is off, LSE/LSI can be configured, HSE/HSI/PLL is off. Except NRST/ PC13-TAMper /PC14-OSC32\_IN/PC15-OSC32\_OUT, most I/O ports are in high resistance state.

In VBAT mode, you can use the following features based on the configuration before the VDD power failure:

- RTC: this can be enabled by the RTCEN bit in register RCC\_BDCTRL

- Internal RC oscillator (LSI RC): can be turned on by the LSIEN bit in register RCC\_CTRLSTS

- External 32.768khz crystal oscillator (LSE OSC): Can be turned on by the LSEEN bit in register RCC\_BDCTRL

- R-SRAM data retention can be enabled by the SR2VBRET bit in register PWR\_CTRL2

## 1.5.1 Enter VBAT mode

When the VDD is powered off, it enters VBAT mode at any time.

## 1.5.2 Exit VBAT mode

When the VDD is restored to the power-on reset threshold, the device exits the VBAT mode. After the VDD is restored, the device core area will be powered on in sequence. After waking up from VBAT mode, code execution is equivalent to reset execution. The VBATF status flag in the power control status register (PWR\_CTRLSTS) indicates that the MCU exits from VBAT mode.

# 2 Power control (PWR)

# 2.1 **Power system introduction**

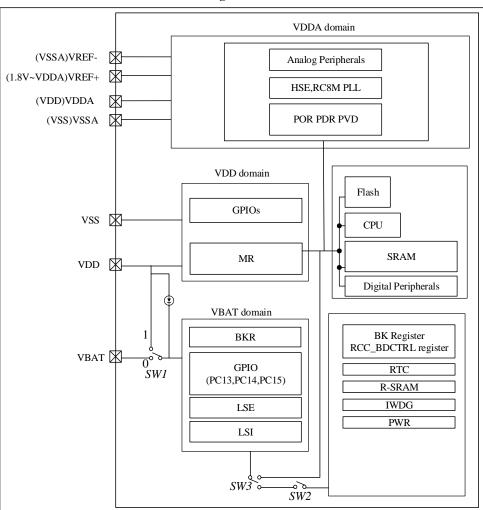

N32G45x, N32G4FR, N32WB452 working voltage (VDD) is 1.8V~3.6V.It mainly has 3 analog/digital power regions (VDD, VBAT, VDDA).See Figure 2-1 power block diagram for details.

As the power control module of the whole device, the main function of the PWR is to control the device into different power modes and can be woken up by other events or interruptions. The N32G45x, N32G4FR, and N32WB452 support RUN, SLEEP, STOP0, STOP2, STANDBY, and VBAT modes.

4/21

Figure 2-1 Power block

## 2.1.1 Power supply

In order to illustrate the functions of different power regions, some power regions are described below. The digital parts of the power regions are described in later chapters of this document.

- VDD domain: voltage input range is 1.8V~3.6V, mainly for MR power input, and for CPU, AHB, APB, SRAM, FLASH and most of the digital peripheral interface power.

- VBAT domain: The input voltage ranges from 1.8V to 3.6V. It supplies power to BKR and some special IO ports (PC13, PC14, PC15). When the VDD is powered off, the switch switches the power supply system VDD to VBAT.

- VDDA domain: Input voltage range 1.8V~3.6V, mainly for the clock and reset system, most analog peripherals power supply.

### 2.1.1.1 Digital module power supply system

The VDD and VBAT input voltages of N32G45x, N32G4FR and N32WB452 range from 1.8V to 3.6V. BKR and MR are internal voltage regulators that can supply power to the digital module power supply system. VDD and VBAT

5/21

are powered by external power supply. VBAT is powered by batteries to keep the contents of the backup area, while VDD is powered by other external power supply systems. In addition, if the battery is not needed, the VBAT must be directly connected to the VDD.

■ MR(RUN,SLEEP,STOP0)

MR is the internal main power controller, mainly used in RUN mode, SLEEP mode and STOP0 mode.MR has two modes, normal mode and low power mode. Low power mode is used for STOP0 to further reduce power consumption.

When the MR enters low power mode, the CPU goes into a deep sleep. The PWR\_CTRL register should be set to PDS bit 0 and LPS bit 1. When MR enters normal mode, you need to set the PDS bit of the PWR\_CTRL register to 0 and the LPS bit to 0.

### ■ BKR(STOP2,STANDBY,VBAT)

The BKR is the internal backup power domain power controller and is used in STOP2, STANDBY, and VBAT modes. In STOP2 mode, the CPU state is maintained, and the digital backup area, GPIO and EXTI are additionally powered. When the CPU enters a deep sleep, set the PWR\_CTRL2 register STOP2S bit to 1.

The main modules in the digital backup area include PWR, IO (PA0\_WAKUP, PC13\_TAMPER, PC14, PC15), R-SRAM, TSC, RTC, BKR, and RCC\_BDCTRL registers. When SW3 is turned on, the CPU enters a deep sleep. When SW1 switches the power supply system to VBAT, VDD is powered off.

## 2.1.2 Backup power domain

During the reset, SW1 switches the power supply system to the VDD power supply area. In STOP2, STANDBY and VBAT modes, the internal voltage regulator BKR will supply power to the digital backup area.

Note:

- The switch between VBAT and VDD remains connected to the VBAT region during the VDD ascent phase or when PDR is detected.

- During the startup phase, if the VDD is quickly established and VDD > VBAT + 0.6V, current can be injected into the VBAT via an internal diode connection. If the power supply or battery connected to VBAT does not support this current injection. It is strongly recommended to place a low voltage diode between the power supply and the VBAT pin.

If there is no external battery in the application. It is recommended that the VBAT pins be connected to the VDD with a 100nF ceramic capacitor. In RUN, SLEEP, and STOP0 modes, the backup area is powered by the VDD (SW1 is connected to the VDD). The following functions are available:

- PC14 and PC15 can be used for normal IO ports or LSE pins

- PC13 can be used with common IO ports, TAMPER pins, RTC parity clock pins, RTC alarm clocks and second outputs

#### Note:

Due to the fact that the current flowing through SW1 and SW2 is limited, the maximum is 3mA.So PA0\_WAKUP, PC13 to PC15 IO output mode is limited, in the external 30PF capacitor, the maximum output speed is 2MHz.In addition, these IO cannot be driven by current, such as LED. The current of SW2 will be maintained at 3mA or lower because GPIO and EXTI work together to consume current. When VBAT supplies power for the backup area, the following functions can be used:

6/21

- PC14 and PC15 can only be used for LSE pins

- PC13 is used for TAMPER pins, RTC alarm clocks, or second outputs

# 2.2 Supply current characteristic

## 2.2.1 General operating conditions

| Symbol             | Parameter                                 | Condition                            | Min  | Max | Unit |

|--------------------|-------------------------------------------|--------------------------------------|------|-----|------|

| f <sub>HCLK</sub>  | Internal AHB clock frequency              | -                                    | 0    | 144 |      |

| f <sub>PCLK1</sub> | Internal APB1 clock frequency             | -                                    | 0    | 36  | MHz  |

| f <sub>PCLK2</sub> | Internal APB2 clock frequency             | -                                    | 0    | 72  |      |

| V <sub>DD</sub>    | Standard operating voltage                | -                                    | 1.8  | 3.6 | V    |

| V <sub>DDA</sub>   | Analog operating voltage                  | Must be the same as $V_{DD}^{(1)}$   | 1.8  | 3.6 | v    |

| VBAT               | Backup operating voltage                  | -                                    | 1.8  | 3.6 | V    |

| т                  | Ambient temperature (Temperature label 7) | Maximum power consumption            | - 40 | 105 | °C   |

| T <sub>A</sub>     | Ambient temperature (Temperature label 7) | Low power consumption <sup>(3)</sup> | - 40 | 125 |      |

| TJ                 | Junction temperature range                | Temperature label 7                  | - 40 | 125 | °C   |

1. It is recommended to use the same power supply for  $V_{DD}$  and  $V_{DDA}$  Power supply, during power up and normal operation,  $V_{DD}$  and  $V_{DDA}$  maximum of 300mV difference is allowed between.

2. If  $T_A$  lower, as long as  $T_J$  no more than  $T_J$ max, a higher PD value is allowed.

3. At lower power dissipation, as long as T<sub>J</sub> no more than T<sub>J</sub>max, T<sub>A</sub> it can be extended to this scope.

4. The above are the working conditions of N32G457 series.

Current consumption is a comprehensive index of a variety of parameters and factors. These parameters and factors include operating voltage, ambient temperature, I/O pin load, product software configuration, operating frequency, I/O pin flip rate, and program in memory The location in and the executed code, etc.

Current consumption measurement method description, see Table 2-1.

All of the current consumption measurements given in this section are performed in a simplified set of code that is equivalent to the Dhrystone 2.1 code.

7/21

### 2.2.2 Maximum current consumption

The microcontroller is under the following conditions:

- All I/O pins are in input mode and connected to a static level V<sub>DD</sub> or V<sub>SS</sub>(No load).

- All peripherals are off unless otherwise noted.

- Flash memory access time adjusted to F<sub>HCLK</sub>(0~32MHz: 0 waiting periods, 32~64MHz: 1 waiting period, 64~ 96 MHz: 2 waiting periods, 96~128MHz: 3 waiting periods, 128~144MHz: 4 waiting periods).

- Instruction prefetch is enabled (note: this parameter must be set before setting the clock and bus divider).

- When the peripheral is turned on:  $f_{PCLK1} = f_{HCLK}/4$ ,  $f_{PCLK2} = f_{HCLK}/2$ .

The parameters given in Table 2-2 and Table 2-3 are based on tests at ambient temperature and VDD supply voltage listed in Table 2-1.

| General         | Parameter                               | Condition                                                  |                   | Max <sup>(1)</sup>     | TL-14 |    |

|-----------------|-----------------------------------------|------------------------------------------------------------|-------------------|------------------------|-------|----|

| Symbol          |                                         |                                                            | f <sub>HCLK</sub> | $T_A = 105 \ ^\circ C$ | Unit  |    |

|                 |                                         |                                                            | 144MHz            | 32                     |       |    |

|                 |                                         | External clock <sup>(2)</sup> .                            | 72MHz             | 18                     |       |    |

| Ŧ               | Supply current in<br>RUN mode<br>Extern | Enable all peripherals                                     | 36MHz             | 11                     |       |    |

| I <sub>DD</sub> |                                         |                                                            |                   | 144MHz                 | 15.8  | mA |

|                 |                                         | External clock <sup>(2)</sup> .<br>Disable all peripherals | 72MHz             | 9.7                    |       |    |

|                 |                                         |                                                            | 36MHz             | 6.7                    |       |    |

#### Table 2-2 Maximum current consumption in RUN mode, data processing code is run from internal flash

1. Derived from comprehensive evaluation and not tested in production.

2. The external clock is 8MHz, PLL is enabled when  $f_{HCLK}{\scriptstyle>}8MHz.$

3. The above are the working conditions of N32G457 series.

#### Table 2-3 Maximum current consumption in SLEEP mode, code running in Flash or RAM

| General         | Parameter                       | Condition                                                 | f <sub>HCLK</sub> | <b>Max</b> <sup>(1)</sup> | Unit |  |

|-----------------|---------------------------------|-----------------------------------------------------------|-------------------|---------------------------|------|--|

| Symbol          |                                 |                                                           |                   | $T_A = 105 \ ^\circ C$    |      |  |

|                 | Supply current in<br>SLEEP mode | External clock <sup>(2)</sup> .<br>Enable all peripherals | 144MHz            | 27                        |      |  |

| Ţ               |                                 |                                                           | 72MHz             | 15.5                      |      |  |

| I <sub>DD</sub> |                                 |                                                           | 36MHz             | 10                        | mA   |  |

|                 |                                 |                                                           | 144MHz            | 9.2                       |      |  |

| E | xternal clock <sup>(2)</sup> . | 72MHz | 6.6 |  |

|---|--------------------------------|-------|-----|--|

|   | Disable all peripherals        | 36MHz | 5.1 |  |

1. Derived from comprehensive evaluation,  $V_{DDmax}$  and  $f_{HCLKmax}$  enable peripheral for conditional test.

2. The external clock is 8MHz, PLL is enabled when  $f_{HCLK}{\scriptstyle>}8MHz.$

3. The above are the working conditions of N32G457 series.

| Symbol               | Parameter                                | Condition                                                                                                                                            | Typical (1)              | Max                   | Unit |

|----------------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------------|------|

| Symbol               | I al ameter                              | Condition                                                                                                                                            | $T_A=25^\circ\mathbb{C}$ | T <sub>A</sub> =105°C |      |

|                      | Supply current in<br>STOP0 mode          | The regulator is in operation mode with<br>low and high speed internal RC oscillators<br>and high speed oscillators off (no<br>independent watchdog) | 300                      | 1200                  |      |

|                      |                                          | The regulator is in low power mode with<br>low and high speed internal RC oscillators<br>and high speed oscillators off (no<br>independent watchdog) | 150                      | 800                   |      |

| I <sub>DD</sub>      | Supply current in<br>STOP2 mode          | The external low speed clock is on, RTC is<br>running, R-SRAM is on, all I/O states are<br>on, and the independent watchdog is off                   | 10                       | 100                   | uA   |

|                      | Supply current in STANDBY mode           | Low speed internal RC oscillator and independent watchdog are on                                                                                     | 3                        | 40                    |      |

|                      |                                          | The low speed internal RC oscillator is on and the independent watchdog is off                                                                       | 2.9                      | 40                    |      |

|                      |                                          | The low speed internal RC oscillator and<br>independent watchdog are closed, and the<br>low speed oscillator and RTC are closed                      | 2.7                      | 3.5                   |      |

| I <sub>DD_VBAT</sub> | Backup<br>domain(VBAT)<br>supply current | The low speed oscillator and RTC are on                                                                                                              | 2                        | 15                    |      |

#### Table 2-4 Typical and maximum current consumption in shutdown and standby mode

1. The typical value is tested at  $V_{DD}/V_{BAT}$  = 3.3V.

2. Derived from comprehensive evaluation and not tested in production.

3. The above are the working conditions of N32G457 series.

## 2.2.3 Typical current consumption

MCU is under the following conditions:

- All I/O pins are in input mode and connected to a static level --  $V_{DD}$  or  $V_{SS}$ (No load).

- All peripherals are off unless otherwise noted.

- Flash memory access time adjusted to F<sub>HCLK</sub>(0~32MHz: 0 waiting periods, 32~64MHz: 1 waiting period, 64~ 96MHZ: 2 waiting periods, 96~128MHz: 3 waiting periods, 128~144MHz: 4 waiting periods).

- Ambient temperature and V<sub>DD</sub> the supply voltage conditions are listed in Table 2-1.

- Instruction prefetch is enabled (note: this parameter must be set before setting the clock and bus divider). When the peripheral is turned on:  $f_{PCLK1} = f_{HCLK}/4$ ,  $f_{PCLK2} = f_{HCLK}/2$ ,  $f_{ADCCLK} = f_{PCLK2}/4$ .

|                 |           | Conditions                                                           |                   | Typical                                  |                         |      |

|-----------------|-----------|----------------------------------------------------------------------|-------------------|------------------------------------------|-------------------------|------|

| Symbol          | Parameter |                                                                      | f <sub>HCLK</sub> | Enable all<br>peripherals <sup>(2)</sup> | Disable all peripherals | Unit |

|                 |           |                                                                      | 144MHz            | 30.3                                     | 14.2                    |      |

|                 | KUN mode  |                                                                      | 72MHz             | 17                                       | 8.1                     | mA   |

|                 |           |                                                                      | 36MHz             | 9.3                                      | 5.3                     |      |

| I <sub>DD</sub> |           | Run on high speed internal                                           | 128MHz            | 30                                       | 12.7                    |      |

|                 |           | RC oscillator (HSI), using<br>AHB predivision to reduce<br>frequency | 72MHz             | 22.5                                     | 7.2                     | mA   |

|                 |           |                                                                      | 36MHz             | 8.8                                      | 3.9                     |      |

#### Table 2-5 Typical current consumption in RUN mode, data processing code is run from internal Flash

1. The typical value is at  $T_A= 25$  °C,  $V_{DD}=3.3$ V.

- 2. An additional 0.8mA of current consumption is added to each analog portion of the ADC. In the application environment, this part of the current is increased only when the ADC is turned ON (setting the ON bit of the ADC\_CTRL2 register).

- 3. The external clock is 8MHz, PLL is enabled when  $f_{HCLK}{\scriptstyle>}8MHz.$

- 4. The above are the working conditions of N32G457 series.

#### Table 2-6 Typical current consumption in SLEEP mode, data processing code is run from internal Flash or RAM

|        |                |            |                   | Туріс                                    |                       |      |

|--------|----------------|------------|-------------------|------------------------------------------|-----------------------|------|

| Symbol | Parameter      | Conditions | f <sub>HCLK</sub> | Enable all<br>peripherals <sup>(2)</sup> | Close all peripherals | Unit |

|        | Supply current |            | 144MHz            | 25.3                                     | 8                     |      |

|                 | in SLEEP |                                                 | 72MHz  | 13.9 | 5.3 |    |

|-----------------|----------|-------------------------------------------------|--------|------|-----|----|

|                 | mode     | External clock <sup>(3)</sup>                   | 36MHz  | 8    | 3.6 | mA |

|                 |          | Run on high speed                               | 128MHz | 24.2 | 6.1 |    |

| I <sub>DD</sub> |          | internal RC oscillator (HSI),                   | 72MHz  | 13.9 | 3.5 |    |

|                 |          | using AHB<br>predivision to reduce<br>frequency | 36MHz  | 7.2  | 2.2 | mA |

1. The typical value is at  $T_A=25$  °C,  $V_{DD}=3.3$ V.

- 2. An additional 0.8mA of current consumption is added to each analog portion of the ADC. In the application environment, this part of the current is increased only when the ADC is turned ON (setting the ON bit of the ADC\_CTRL2 register).

- 3. The external clock is 8MHz, PLL is enabled when  $f_{HCLK}$  >8MHz.

- 4. The above are the working conditions of N32G457 series.

# 3 Hardware environment

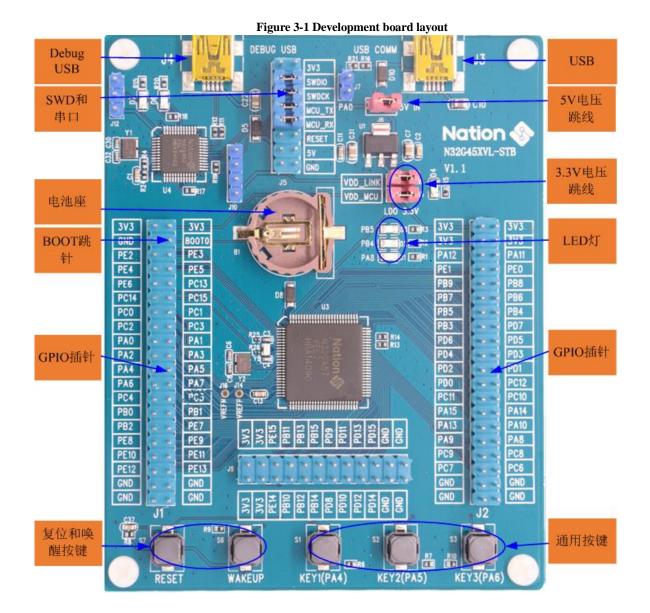

# 3.1 **Development board layout**

#### 1) Power supply for development board

The development board can be powered by USB interface (J3) and Debug USB (J4), connected to 3.3V LDO input port through J6 jumper.

#### 2) USB port (J3)

Mini USB interface (J3), connected to MCU DP DM, can be used for USB interface communication.

12/21

#### 3) Debug USB (J4)

The MCU can be used to download programs through the Debug USB or as a serial port.

#### 4) SWD Interface (J5)

SWD interface can also be used for program download debugging, using ULINK2 or JLINK to download programs to the chip. You can also use the jumper to short SWDIO and SWDCK, and use the Debug USB to download programs.

#### 5) Reset and wake up buttons (S7, S6)

S7 and S6 are reset buttons and wake buttons respectively, which are connected to NRST pins and PA0-WKUP pins of the chip respectively for chip reset and wake functions.

#### 6) Universal keys (S1, S2, S3)

S1, S2 and S3 are respectively connected to PA4, PA5 and PA6 pins of the chip.

#### 7) Battery holder (BAT)

A CR1220 battery can be placed in the battery holder, which is connected to the chip VBAT pin to provide power.

#### 8) **GPIO** port (J1, J2)

All the GPIO interfaces of the chip are elicited, and 3.3V voltage and GND pins are reserved on the pins for easy testing. See N32G45x Series Data Manual, DS\_N32G4FR Series Data Manual, DS\_N32WB452 Series Data Manual for the specific definition of the interface.

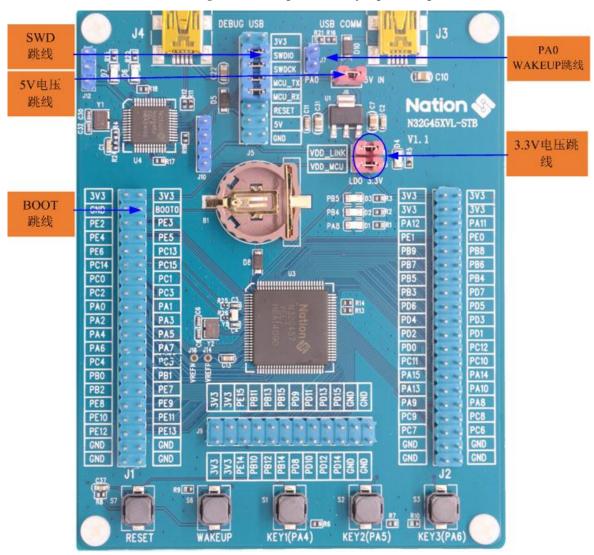

# 3.2 **Development board jumper instructions**

#### Figure 3-2 Development board jumper description

Jumper descriptions are as follows:

| No. | Jump line item number | Jump line function        | Directions                                                                                              |

|-----|-----------------------|---------------------------|---------------------------------------------------------------------------------------------------------|

| 1   | J6                    | 5V voltage jumper         | The J6 jumper connects the J3 and J4 USB ports and supplies power to the LDO3.3V input port.            |

| 2   | J8 and J15            | 3.3V power supply jumper  | J8: Supply 3.3V power to NS-LINK MCU chip.<br>J15: Supply 3.3V power to main MCU chip.                  |

| 3   | J5                    | SWD jumper, Serial jumper | Use NS-LINK to download program to MCU<br>through USB Debug port, need to short SWDIO<br>and SWDCK pin. |

14/21

|  | When using NS-LINK as a serial port through |

|--|---------------------------------------------|

|  | the USB Debug port, the two pins MCU_TX     |

|  | and MCU_RX need to be short-circuited.      |

# 3.3 **Development board schematic diagram**

N32G45XML-STB Development board schematic see N32G45XVL-STB\_V1.1

# 4 Programming instructions

# 4.1 Set SLEEP mode

Open the SLEEP project in SDK. The part in circle ① in Figure 4-1 is the API function to enter SLEEP mode. After compiling, download it to the development board.

File Edit View Project Flash Debug Peripherals Tools SVCS Window Help 🕞 🗟 🥐 🔍 - 💊 🔿 🔗 🗋 🚰 🛃 🐉 👗 🏝 🛍 🖃 🗠 🖛 🛶 🥐 🎘 🤼 👯 🏥 🐺 //注 //提 💆 SystemInit 🕞 🐔 📥 ≒ 🗇 幽 main.c Main.h User\_Key\_Config.c User\_LED\_Config.c n32g45x\_it.c Project д 🔝 49 void delay(vu32 ∩Count) 50 ⊟ { 🖃 🍄 Project: SLEEP 🖃 ᇶ N32G45x 51 vu32 · index ·= · 0; E STARTUP 52 for (index = (34000 \* nCount); index != 0; index--) 🗄 🚞 CMSIS 53 -54 -55 } 1 1 1 **4** 🗄 🚞 FWLB 3 🖨 🦾 USER 56 🗄 📄 main.c 58 . \* · @brief · · Main · program. 59 . \*/ 🗄 📄 n32g45x\_it.c User\_Key\_Conf 🗄 📄 User\_LED\_Con 60 int main (void) 61 🕀 { 🖨 🦾 DOC 62 🗄 · · · · /\*!< · At · this · stage · the · microcontroller · clock · setting · is · already · configu - readme.txt 63  $\texttt{this} \cdot \texttt{is} \cdot \texttt{done} \cdot \texttt{through} \cdot \texttt{SystemInit()} \cdot \texttt{function} \cdot \texttt{which} \cdot \texttt{is} \cdot \texttt{called} \cdot \texttt{from} \cdot \texttt{s}$ 🗄 🚞 LOG 64  $\cdot \cdot \texttt{file} \cdot (\texttt{startup}\_\texttt{n32g45x}\_\texttt{xx},\texttt{s}) \cdot \texttt{before} \cdot \texttt{to} \cdot \texttt{branch} \cdot \texttt{to} \cdot \texttt{application} \cdot \texttt{main}.$ 65 ······To·reconfigure·the·default·setting·of·SystemInit()·function, ·refe 66 system\_n32g45x.c file 67 . . . . \*/ 68 log\_init(); 69 70 71 RCC\_EnableAPB1PeriphClk(RCC\_APB1\_PERIPH\_PWR, ENABLE); 72 /\* Initialize LEDs on n32g45x-EVAL board \*/ 73 74 LEDInit(LED1\_PORT,LED1\_PIN); LEDInit(LED3\_PORT,LED3\_PIN); 75 LEDOff(LED1\_PORT,LED1\_PIN); 76 77 LEDOff(LED3\_PORT,LED3\_PIN); /\* Initialize Key button Interrupt to wake up the low power\*/ 78 KeyInputExtiInit(KEY INPUT PORT, KEY INPUT PIN); 79 /\* Clear the Interrupt flag \*/ 80 EXTI\_ClrITPendBit(EXTI\_LINE0); 81 DBG\_ConfigPeriph(DBG\_SLEEP, ENABLE); 82 while (1) 83 🖨 · · { 84 /\* .Turn .on .LED3 .\*/ 85 LEDBlink(LED3 PORT, LED3 PIN); 86 /\* Insert a long delay \*/ 87 delav(60);

/\* Request to enter SLEEP mode\* 88 (1)PWR\_EnterSLEEPMode(SLEEP\_NOW, PWR\_STOPENTRY\_WFI); 89 90 - 3 91 } 92

Figure 4-1 SLEEP entering Settings

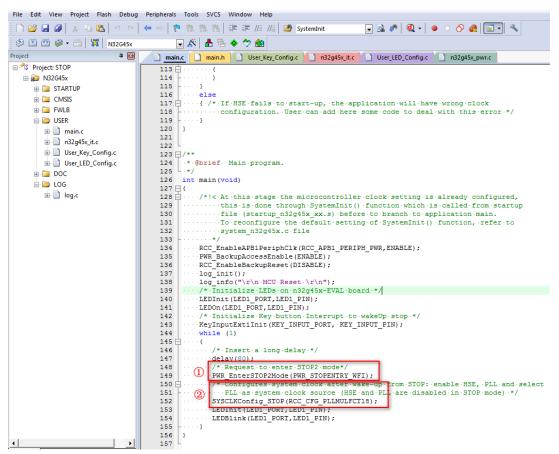

# 4.2 Set STOP2 mode

STOP2 mode is based on the Cortex-M4 deep sleep mode, and all the core digital logic areas are powered off. Main voltage regulator (MR) is off, HSE/HSI/PLL is off. CPU registers are maintained, LSE/LSI can be configured, GPIO is maintained, and peripheral I/O multiplexing is not maintained.16K bytes of R-SRAM remain, and other SRAM and register data are lost.84-byte backup register hold. GPIO and EXTI are enabled.

Open the STOP2 project in the SDK, the part circled in Figure 4-2 is the API function to enter STOP2, this function will set the interrupt to enter STOP2, the part ② in the circle in Figure 4-2 is to switch the system clock back to the system when exiting the STOP2 mode high-speed clock. This mode needs to pay attention to the change of the system clock, so the peripherals need to be reconfigured according to the actual clock source.

Figure 4-2 STOP2 enter Settings

## 4.3 Set STOP0 mode

STOP0 mode is based on the Cortex®-M4 deep sleep mode, combined with the peripheral clock control mechanism. The voltage regulator can be configured for normal or low power mode. In STOP0 mode, most clock sources in the core domain, such as PLL, HSI, and HSE, are disabled. But SRAM, R-SRAM, and all register contents are saved.

In STOP0 mode, all I/O pins remain in the same state as in run mode.

Open the STOP0 project in the SDK, the part circled in Figure 4-3 is the API function to enter STOP0, this function

17/21

will set the interrupt to enter STOP0, the part ② in the circle in Figure 4-3 is to switch the system clock back to the system when exiting the STOP0 mode high-speed clock. This mode needs to pay attention to the change of the system clock, so the peripherals need to be reconfigured according to the actual clock source.

|                                    | Figure 4-3 STOP0 entering Settings                                                                  |  |  |

|------------------------------------|-----------------------------------------------------------------------------------------------------|--|--|

| File Edit View Project Flash Debug | J Peripherals Tools SVCS Window Help                                                                |  |  |

| 🗋 🗋 🛃 🌒 🐰 🛍 🛍 🖉 🗠                  | ← →   隆 🐘 🐘   幸 幸 //= //E   🖉 SystemInit 🕢 💽 🗟 🌮   @ •   ● ○ 🔗 🍓 💷 • 🔦                              |  |  |

| 🕸 🕮 🎬 🐳 - 🔜 🙀 N32G45x              | 🖵 🔊 🚠 🗟 🗇 🏟                                                                                         |  |  |

| Project 🛛 📮 🔟                      | main.c main.h User_Key_Config.c n32g45x_it.c User_LED_Config.c n32g45x_pwr.c readme.txt             |  |  |

| E Project: STOP                    | 112                                                                                                 |  |  |

| 🖻 ᇶ N32G45x                        | 113                                                                                                 |  |  |

| 🗉 🛄 STARTUP                        | 114                                                                                                 |  |  |

| 🖃 🗁 CMSIS                          | 115 -····}<br>116 ····else                                                                          |  |  |

|                                    | 110 ···································                                                             |  |  |

| H 📮 FWLB                           | 11. 11. 11. 11. 11. 11. 11. 11. 11. 11.                                                             |  |  |

|                                    | 119 - · · · · }                                                                                     |  |  |

| main.c                             | 120 }                                                                                               |  |  |

|                                    | 121                                                                                                 |  |  |

|                                    | 122 L<br>123 P/**                                                                                   |  |  |

|                                    | 123 - / **<br>124 ·*·@brief··Main·program.                                                          |  |  |

| · ⊡ User_LED_Config.c              |                                                                                                     |  |  |

| E DOC                              | 126 int main (void)                                                                                 |  |  |

| readme.txt                         | 127 🖵 {                                                                                             |  |  |

| E LOG                              | 128 =                                                                                               |  |  |

| ie∭ log.c                          |                                                                                                     |  |  |

|                                    | 131To reconfigure the default setting of SystemInit() function, refer to                            |  |  |

|                                    | 132system_n32g45x.c.file                                                                            |  |  |

|                                    | 133*/                                                                                               |  |  |

|                                    | 134 CC EnableAPB1PeriphClk(RCC APB1_PERIPH_PWR, ENABLE);                                            |  |  |

|                                    | 135 ····PWR_BackupAccessEnable(ENABLE);<br>136 ····RCC EnableBackupReset(DISABLE);                  |  |  |

|                                    | 137 ····log init();                                                                                 |  |  |

|                                    | 138log info("\r\n.MCU.Reset.\r\n");                                                                 |  |  |

|                                    | 139 ····/*·Initialize·LEDs·on·n32g45x-EVAL·board·*/                                                 |  |  |

|                                    | 140LEDInit (LED1_PORT, LED1_PIN);                                                                   |  |  |

|                                    | 141 ····LEDOFf(LED1_PORT,LED1_PIN);<br>142 ····/*·Initialize·Key·button·Interrupt·to·wakeUp·stop·*/ |  |  |

|                                    | 143 ····KeyInputExtiInit(KEY INPUT PORT, KEY INPUT PIN);                                            |  |  |

|                                    | 144while (1)                                                                                        |  |  |

|                                    | 145 [ {                                                                                             |  |  |

|                                    | 146 ·····/*·Insert·a·long·delay·*/                                                                  |  |  |

|                                    | 147 ······delay(80);<br>148 ····································                                    |  |  |

|                                    | 148                                                                                                 |  |  |

|                                    | 150                                                                                                 |  |  |

|                                    | 151PLL-as-system-clock-source-(HSE-and-PLL_are-disabled-in-STOP-mode) */                            |  |  |

|                                    | 152 ····②· SYSCLKConfig_STOP(RCC_CFG_PLLMULFCT18);                                                  |  |  |

|                                    | 153 LEDBIINK (LEDI_PORT, LEDI_PIN);                                                                 |  |  |

|                                    | 154}                                                                                                |  |  |

| 1                                  | 155 J                                                                                               |  |  |

|                                    |                                                                                                     |  |  |

#### Figure 4-3 STOP0 entering Settings

#### 4.4 Set STANDBY mode

STANDBY mode can achieve lower power consumption, it is based on Cortex®-M4 deep sleep mode, the core domain is completely turned off, and the backup power domain is turned on to supply power to VDD and BKR.

Open the STANDBY project in the SDK, the part circled in Figure 4-4 is the API function to enter STANDBY, this function will set the interrupt to enter STANDBY.

| Figure ++ 51A(0) F chiefing Security |                                                                              |  |  |

|--------------------------------------|------------------------------------------------------------------------------|--|--|

| File Edit View Project Flash D       | ebug Peripherals Tools SVCS Window Help                                      |  |  |

|                                      | ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○                                        |  |  |

| 🕴 🏝 🛗 🧼 🗸 🔣 🙀 N32G                   | 45x 💽 🔊 📥 🗟 🗇 🍪                                                              |  |  |

| Project 🛛 🗜 🔟                        | main.c User_LED_Config.c                                                     |  |  |

| 🖃 🔧 Project: STANDBY                 | 58 ->                                                                        |  |  |

| 🖻 🚂 N32G45x                          | 59 戸/**                                                                      |  |  |

| STARTUP                              | 60 ·*·@brief··Main·program.                                                  |  |  |

|                                      | 61 - */                                                                      |  |  |

| FWLB                                 | 62 int main (void)                                                           |  |  |

| USER                                 | 63 - {<br>64 ····/*Clean·backup·flag·to·exit·debug·mode·*/                   |  |  |

|                                      | 65 ····RCC EnableAPB1PeriphClk(RCC APB1 PERIPH PWR,ENABLE);                  |  |  |

| 💼 👘 main.c                           | 66 PWR BackupAccessEnable (ENABLE);                                          |  |  |

|                                      | 67 RCC_EnableBackupReset (DISABLE);                                          |  |  |

| User_LED_Config.c                    | 68 ····log_init();                                                           |  |  |

| E DOC                                | 69 ····log_info("\r\n·MCU·Reset·\r\n");                                      |  |  |

| readme.txt                           | 70 ····/*·Initialize·LEDs·*/                                                 |  |  |

| 🗄 🛅 LOG                              | 71 ····LEDInit(LED1_PORT, LED1_PIN);<br>72 ····LEDInit(LED3 PORT, LED3 PIN); |  |  |

|                                      | 73 ····/*·Turn·on·LED1·*/                                                    |  |  |

|                                      | 74 LEDON (LED1 PORT, LED1 PIN);                                              |  |  |

|                                      | 75 ····LEDOn (LED3_PORT, ·LED3_PIN);                                         |  |  |

|                                      | 76 ····/*·Enable·FWR·and·BKF·clock·*/                                        |  |  |

|                                      | 77 RCC_EnableAPB1PeriphClk(RCC_APB1_PERIPH_PWR, ENABLE);                     |  |  |

|                                      | 78 ····/*·Enable·WKUP·pin·*/                                                 |  |  |

|                                      | 79 ···· PWR_WakeUpPinEnable(ENABLE);<br>80 ····while (1)                     |  |  |

|                                      | 81 - · · · · {                                                               |  |  |

|                                      | 82 ·····/*·Check·if·the·Wake-Up·flag·is·set·*/                               |  |  |

|                                      | 83 ·····if · (PWR_GetFlagStatus(PWR_WU_FLAG) · != · RESET)                   |  |  |

|                                      | 84 🔁 · · · · · · {                                                           |  |  |

|                                      | 85 ·····/*·Clear·Wake·Up·flag·*/                                             |  |  |

|                                      | 86PWR_ClearFlag(PWR_WU_FLAG);<br>87                                          |  |  |

|                                      | 88 ·····/*·Delay·a·long·time·*/                                              |  |  |

|                                      | 89 ······Delay(600);                                                         |  |  |

|                                      | 90                                                                           |  |  |

|                                      | 91 (1) FWR EnterStandbyState();                                              |  |  |

|                                      | 92 - · · · · }                                                               |  |  |

|                                      | 93 }                                                                         |  |  |

|                                      | 94 L<br>95 🖂 / * *                                                           |  |  |

| I I                                  |                                                                              |  |  |

#### Figure 4-4 STANDBY entering Settings

# 5 Version history

| Version | Date     | Note                                                                                                                                                                  |

|---------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V1.0    | 2021-8-6 | Create the document                                                                                                                                                   |

| V1.1    | 2022-7-6 | <ol> <li>Update the power supply block diagram</li> <li>Add remarks about the operating conditions of<br/>N32G457 series</li> <li>Optimize the description</li> </ol> |

0/21 Nations Technologies Inc. Tel: +86-755-86309900 Email: info@nationstech.com Address: Nations Tower, #109 Baoshen Road, Hi-tech Park North. Nanshan District, Shenzhen, 518057, P.R.China

20/21

# 6 Legal Notice

This document is the exclusive property of Nations Technologies Inc. (Hereinafter referred to as NATIONS). This document, and the product of NATIONS described herein (Hereinafter referred to as the Product) are owned by NATIONS under the laws and treaties of the People's Republic of China and other applicable jurisdictions worldwide. NATIONS does not grant any license under its patents, copyrights, trademarks, or other intellectual property rights. Names and brands of third party may be mentioned or referred thereto (if any) for identification purposes only.

NATIONS reserves the right to make changes, corrections, enhancements, modifications, and improvements to this document at any time without notice. Please contact NATIONS and obtain the latest version of this document before placing orders.

Although NATIONS has attempted to provide accurate and reliable information, NATIONS assumes no responsibility for the accuracy and reliability of this document.

It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. In no event shall NATIONS be liable for any direct, indirect, incidental, special, exemplary, or consequential damages arising in any way out of the use of this document or the Product.

NATIONS Products are neither intended nor warranted for usage in systems or equipment, any malfunction or failure of which may cause loss of human life, bodily injury or severe property damage. Such applications are deemed, "Insecure Usage".

Insecure usage includes, but is not limited to: equipment for surgical implementation, atomic energy control instruments, airplane or spaceship instruments, all types of safety devices, and other applications intended to support or sustain life.

All Insecure Usage shall be made at user's risk. User shall indemnify NATIONS and hold NATIONS harmless from and against all claims, costs, damages, and other liabilities, arising from or related to any customer's Insecure Usage. Any express or implied warranty with regard to this document or the Product, including, but not limited to, the warranties of merchantability, fitness for a particular purpose and non-infringement are disclaimed to the fullest extent permitted by law.

Unless otherwise explicitly permitted by NATIONS, anyone may not use, duplicate, modify, transcribe or otherwise distribute this document for any purposes, in whole or in part.

Nations Technologies Inc.

Tel: +86-755-86309900

Email: info@nationstech.com

Address: Nations Tower, #109 Baoshen Road, Hi-tech Park North.

Nanshan District, Shenzhen, 518057, P.R.China

21/21